# A Magnetically Coupled Converter Connected Three Phase Voltage Source Inverter for EV Applications

P. Booma Devi\*, M.Vijayasarathy\*\*, Latha\*\*\*

\* Department of Electrical and Electronics Engg. SSM Institute of Engineering & Technology, Dindigul, India.

\*\* Department of Electrical and Electronics Engg, Nandanam College of Engineering, Vellore, India.

\*\*\*Satyabhama University, OMR road, Chennai India.

Abstract— The Electrical Vehicle (EV) is an obligatory segment is current era, due the shortage of fossil fuel and increasing CO2 emissions. In EV the vehicles drive is consuming more energy than other part of vehicle appliances. The medium voltage EV drives need 400 to 600V DC-link for their full range operation. Hence, the high step DC to DC converter is obvious to required DClink voltage of the VSI, which is need to give a gain higher range of voltage gain since vehicle battery is only in the arrange of 24 V to 48 V. With this aim a nonisolated DC to DC converter is proposes here for EV VSI drive. The DC to DC converter is operating based on transformer coupled and contains only one capacitor with tightly-coupled 3 winding transformer inductor arrangement. Hence, proposed magnetically coupled DC to DC converter able to provide higher voltage gain varies with different winding factors, and duty cycles. Thus comparing with other existing DC to DC converter, the proposed one has more control degrees of freedom in terms its voltage gain. The converter with lesser energy storage elements, the converter has boosted the DC nearly 12 times. Also it has, and therefore, improving the drive versatility is high. The PWM switching techniques are introduced to this converter fed VSI topology to control drive. The working principle of the proposed transformer based DC to DC Source fed VSI is analysed and simulated using MATLAB/Simulink system software. The laboratory based small scale 200W power circuit is designed and developed and the control algorithm is implemented in PIC microcontroller platform. The Analysis, simulation and experimentation validating the proposed converter fed VSI drive system for EV applications.

Keywords— Transformer based in high step DC to DC converter, impedance networks, voltage source inverter.

# I. INTRODUCTION

The Electrical Vehicle (EV) is a more focused electrical load for the future electrifies per capita for the world. The association is estimated 20% IC engine vehicles is migrated EVs and they are going to play in the road in 2020. In EV the vehicles drive is consuming more energy

than other part of vehicle appliances [1]. The EV drives mainly used induction motor, permanent magnet synchronous motor, or BLDC motor. These motor are normally either in low voltage machines or high voltage machine. There many literatures on DC to DC converter fed VSI drive for variable DC bus voltage [2, 3]. The research papers are mainly focused power converters design and its controller arguments to improve system efficiency of the EV. The aim of a variable DC-link bus voltage for VSI is to get better the system controllability and efficiency by boosting the DC-bus voltage for the period of flux-weakening in the motor drive. In fluxweakening operation state, a restricted DC-bus voltage results in involving a negative d-axis current to weaken the flux. To achieve this high voltage gain DC-DC converter employed with inverter [4, 5, 33]. The High step voltage gain DC to DC converter is a principle follows Z-source network [6]. The attempt is made for involving multilevel inverters for PV connected stand alone and grid connected applications [7-10]. There are many research has been reported in Z-source network, which are mainly developed to offer an efficient power conversion with an extensive voltage gain [11]. The upgrading to the impedance networks realizing for higher voltage boosting through the coupled magnetic circuit. These power circuits control is variant based on their inductor arrangement and shootthrough time [12]-[14]. The coupled magnetic circuit based DC to DC conversion, verity of converter is proposed ( $\Gamma$ [15], T [16], trans-Z [17], TZ [18], LCCT-Z- [19], transformer-isolated [20], and Y [21]) and they are mainly structured based on inductors and capacitors. The work is also carried out for maintain the voltage stability for adding the battery across the capacitor. Through these idea is improving the system stability, the cost and size does not comprehend [22]. The authors, Y. P. Siwakoti et.al in [23], suggested the interesting high step voltage conversion DC to DC converter for distributed power system which improves overall system reliability. In this work, by varying the voltage gain through changing the transformer ratio. The converter has been designed and operated for the specific duty-cycle interval and hence the converter maintain their controllability. For controlling inverter along with Z-source network many PWM techniques are developed which are mainly giving interest to create a

short through (ST). These ST attempt has been done for both sine PWM (SPWM) and space vector PWM (SVPWM) [ 24,25,31,37]. Among SPWM is simple and easy to implement. The selective harmonics eliminations and 3<sup>rd</sup> order harmonics elimination is a next candidates to addressing the inverter performance with respect to harmonics cancelations [26]. The paper dealt the converter with 3rd order harmonics in a PV application including ST creations [27, 28]. Normally magnetic coupled converter fed VSI drive suffered with higher voltage and current harmonics, which are main causes of the EV drive nonsmoother performances [32]. This dreadful behaviour VSI DC-link voltage is supplied through the front end converter circuit inductor. Hence the special attendance is necessary for taking care of the input voltage and current harmonics components [29, 34]. .

Based on the clear discussion on the EV drive requirements, the high step DC to DC converter to meet out the DC-link requirement of the VSI. In addition, the EV drive needs high efficient and smoother acceleration. Henceforth, in this paper proposes a three winding magnetically coupled transformer structure DC to DC converter fed three phase voltage source inverter for EV drive. The suggested power circuitry is able to provide a continuous DC-voltage to the VSI for the full range of vehicle drive curve requirements. The paper also deals the design and circuit operation of the proposed power circuitry. The working principle of the proposed transformer based DC to DC Source fed VSI is analysed and simulated using MATLAB/Simulink system software. The laboratory based small scale 200W power circuit is designed and developed and the control algorithm is implemented in PIC microcontroller platform. The Analysis, simulation and experimentation validating the proposed converter fed VSI drive system for EV applications.

#### II. EV DRIVE SYSTEM REVIEW

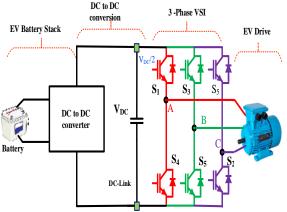

A typical EV motor drive system consists of a threephase VSI and a motor as shown in Fig 1. In an EV the DC- bus voltage of the VSI is generated from the EV inbuilt battery in a straight line through a DC to DC boost converter [3].

Fig 1. Classical EV drive power system

The battery connected EV another task is to maintain the battery energy management and power handling. Precisely determining the SOC of the battery over time is crucial for the performance of intellectual battery management approaches. The DC to DC converter selection is important segment in the EV electrical drive, since they need to fix the DC –link voltage for the inverter.

## III. MAGNETICALLY COUPLED DC TO DC CONVERTER

# 1. Magnetically coupled DC to DC converter topological structure

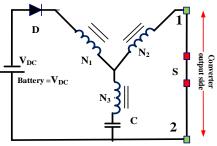

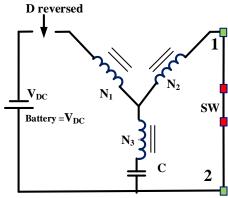

A typical magnetic coupled DC to DC converter system as shown in Fig 1. The converter is consist of three magnetic coupled with different winging and inductor range. The input diode is used to connect input DC source and three magnetic coupled inductors. The capacitor is used to source the supply to output inductor in non-ST states. The converter is shaped as Y-shape consists of a DC input supply, a Y-source impedance network (a three winding coupled inductor / transformer and a capacitor) in addition to an inverter bridge. Y-source network comprises of a passive diode, D, a winding coupled inductor  $(N_1:N_2:N_3)$  along with a capacitor, C. The effectiveness of the inverter depends on the magnetic coupling tightness between the coupled inductors to keep away from any losses through leakage inductances.

Fig 2. Magnetically coupled DC to DC converter [23]

The Y-source impedance function can be explained by a simple single switch converter as shown in the Fig 2. Considering the network working in ideal operating conditions the converter will either be in its shoot-through state or non-shoot-through state while ignoring their leakage inductances. For the shoot-through state, switch S is turned ON to short terminals 1 and 2, which in turn, sources diode, D in the association to reverse bias. The converter is bring back to the non-ST state by turned OFF the switch, S with the diode, D conducting. Averaging voltage across the magnetizing inductance for these two states results in the peak DC-link voltage V<sub>12</sub>, across terminals 1 and 2 in terms of input DC voltage to the VSI. Nevertheless this can be accomplished only with ideal operating situation where the leakage inductances, L<sub>1</sub> of the network is nullified or significantly reduced. The Minimization of L<sub>l</sub> is not constantly feasible or costeffective as it needs more superior core as well as windings. Consequently effects caused by the leakage inductances must be studied thoroughly.

# Magnetically coupled DC to DC converter mode of operations

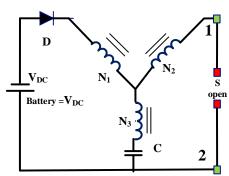

Fig 3. At Non-ST, D forward Biased

Fig 4. At ST, D forward Biased, )Intermediate state

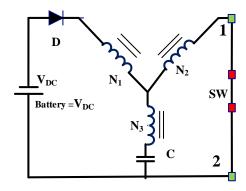

Fig. 5. At ST, D reversed Biased

## 2.1 Modes of operation

An intermediate equivalent circuit is introduced when the impedance source transits from non-ST state to ST state as shown in Fig. 4. During non-ST state inductances are all discharging energies as well as current is therefore decreasing. The shunt switch S in the fig.3 is next shorted, which ideally, will lead to the ST circuit shown in Fig. 5. Nevertheless, for the non-ideal case, an intermediate circuit shown Fig. 5 will be inserted for a short time interval, sourced by the rapid fall of the current through leakage inductance,  $L_1$  in  $N_1$ , and rapid increases of currents during leakage inductances  $N_2$  and  $N_3$ . The intermediate state ends only as the leakage current through

N<sub>1</sub>and diode D reduced to zero. For ST to non-ST transition, the network is in its ST state, when the switch, S is turned OFF, the network attached the source to the load and transits to non-ST state. Unlike the forward conduction, there is no intermediate state and the network enters its non-ST state directly with diode, D conducting, though its current may rises rapidly in excess of a short duration slightly than step-increased. No reduction of the ST duration is therefore introduced by the reverse transition.

The current strained via this capacitive load be able to adapt to leakage current at instantaneous commutation, therefore neither voltage spikes nor limitations are practiced with capacitive loads. At less inductive nature, during the commutation from ST state to non-ST state, leakage currents caused by leakage inductance in  $N_3$  will be draped down to current directly, ensuing in high voltage in the circuit. Beside this momentary is not mitigated, it may affect  $N_1$  and  $N_2$  the leakage currents. Therefore a capacitive-snubber may be additional in order to transport downward between the load current and leakage current.

# 2.2 Deign and modelling the dc output voltage control

At the ST state interval d<sub>ST</sub>, while the switch S is "ON" and diode, D is reverse-biased, the expression as,

$$V_{C1} + \frac{V_L}{n_{12}} - \frac{V_L}{n_{13}} = 0 \tag{1}$$

Where,  $n_{13} = N_1/N_3$ ,  $n_{12}=N_1/N_2$ , as well as voltage across the inductor is given as,

$$V_L = V_{C1} \left( \frac{n_{13} n_{12}}{n_{12} - n_{13}} \right) \tag{2}$$

At non-ST state, the interval (1  $\text{-d}_{ST}$ ), diode, D is conducting is conducting source to the load, the KVL expression for  $V_L$ ,

$$V_{c1} + V_L + \frac{V_L}{n_{12}} = V_{DC} \tag{3}$$

$$V_{L} = \left[ V_{DC} - V_{C} \right] \left( \frac{n_{12}}{1 + n_{12}} \right) \tag{4}$$

The voltage across the capacitor, V<sub>C</sub> can be derived as,

$$V_{C1}\left(\frac{n_{13} * n_{12}}{n_{12} - n_{13}}\right) (d_{ST}) + \left\{ \left[V_{DC} - V_{C}\right] \frac{n_{12}}{n_{12} + 1} \right\} (1 - d_{ST}) = 0 \quad (5)$$

From the Eq.(6), the capacitor voltage across, V<sub>C</sub>,

$$V_{C} = \frac{V_{DC} (1 - d_{ST})}{\left[1 - \frac{n_{12} d_{ST} (1 + n_{13})}{(n_{12} - n_{13})}\right]}$$

(6)

At the non-ST states,

$$V_{dc\_link} = V_{DC} - V_{L} + \frac{V_{L}}{n_{13}}$$

(7)

$$V_{dc\_link} = \frac{V_{in}}{1 - Fd_{ST}}; F = \left(\frac{N_3 + N_1}{N_3 - N_2}\right)$$

(8)

$$N_1 + 2 N_2 > N_3$$

;  $N_3 - N_2 > 0$ ;  $N_2 < N_3$ ;  $N_3 > 1$

$$0 < 1 - Fd_{ST} \le 1$$

;  $0 \le d_{ST} \le d_{ST \max} = 1/k$

$BF = 1.15 (1 - d_{ST})$  (9)

The Magnetically coupled DC to DC converter voltage gain varies with different winding factors, BF and ST duty cycles d<sub>ST.</sub> The desired converter gain with various different arrangements of BF and  $d_{\text{ST}}$ . Table 1. illustrates K and d<sub>ST</sub> for selection of converter voltage gain. The table shows the clear combination of BF, d<sub>ST</sub>, voltage gain, N<sub>1</sub>:  $N_2$ :  $N_3$ .

Controlling d<sub>ST</sub> and coupled inductor N<sub>1</sub>,N<sub>2</sub> and N<sub>3</sub>, the output voltage of the converter can control in full degree of freedom.

Table 1 – converter parameter F,  $d_{ST}$ , voltage gain,  $N_1$ :  $N_2$ :

|   |                          | 1\3                         |                                                |

|---|--------------------------|-----------------------------|------------------------------------------------|

| K | $0 < d_{st} < d_{stmax}$ | Voltage Gain,G <sub>v</sub> | N <sub>1</sub> :N <sub>2</sub> :N <sub>3</sub> |

| 2 | $0 \le d_{ST} \le 1/2$   | $0.5M(1-2d_{ST})^{-1}$      | 1:1:3,                                         |

|   |                          |                             | 2:1:4,                                         |

|   |                          |                             | 1:2:5, 3:1:5                                   |

| 3 | $0 \le d_{ST} \le 1/3$   | $0.5M(1-2d_{ST})^{-1}$      | 1:1:2,                                         |

|   |                          |                             | 3:1:3,                                         |

|   |                          |                             | 2:2:4, 1:3:5                                   |

| 4 | $0 \leq d_{ST} \leq 1/4$ | $0.5M(1-2d_{ST})^{-1}$      | 2:1:2,                                         |

|   |                          |                             | 1:2:3,                                         |

|   |                          |                             | 5:1:3, 4:2:4                                   |

| 5 | $0 \le d_{ST} \le 1/5$   | $0.5M(1-2d_{ST})^{-1}$      | 3:1:2,                                         |

|   |                          |                             | 2:2:3,                                         |

|   |                          |                             | 1:3:4, 7:1:3                                   |

| 6 | $0 \leq d_{ST} \leq 1/6$ | $0.5M(1-2d_{ST})^{-1}$      | 4:1:2,                                         |

|   |                          |                             | 3:2:3,                                         |

|   |                          |                             | 2:3:4, 1:4:5                                   |

The gain produced by the Y -source network is thus a combination of those expected from the T - or trans-Zsource and  $\Gamma$  -source networks. This either creates a higher gain or allows merits of the other networks to be flexibly merged. The latter can be helpful when subject to size and type availabilities while choosing magnetic core, wire and coupling method for winding the transformer. The goal is to maximize coupling, and hence minimize leakage, which if not ensured, will lead to higher switching voltage in addition to a reduction in gain.

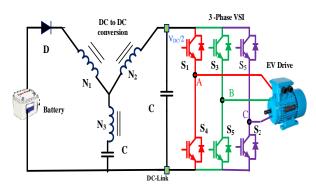

# IV. DC TO DC CONVERTER CONNECTED VSI

The Fig. 6 show the DC to DC converter connected VSI. Here the magnetically coupled DC to DC converter is connected with three phase six inverter. The three-phase VSI consists of six semiconductor switches ( $T_1$  to  $T_6$ ) with 180-degree phase shift conduction among their upper and lower leg power electronics controlled switches. The VSI operates through six intervals with 60 degree interval each. For 60 degree every interval one upper as well as two lowers, or two upper with one lower switch are tuned ON and OFF for providing symmetry operation. In this way in totally eight possible combinations of ON and OFF switching operations form the one cycle three phase VSI output voltage and current. For example, switching representation of this state is used as [000] in mode-1 where all upper switches are "OFF". Similarly, for [101], phase A-leg and phase C leg upper switch are "ON", and

phase B-leg lower switch is considered as "OFF". The table 2 illustrates entire switching modes VSI and also representing the corresponding phase and line voltages. Including two ([111], [000]) zero vector modes and six non-zero states, the VSI forms eight possible switching combinations.

Fig 6. Magnetically coupled DC to DC converter with VSI fed drive

The ST is created using shorting same leg inverter. Example, the  $S_1$  and  $S_2$  is turned ON in the same time the converter is behave a ST mode operation. During the non-ST, the VSI is following the table-2 (regular switching operations)

Table 2. VSI switching vector, phase voltage and line voltage.

| Mode | Volta<br>ge | Line to Line<br>voltage |                 |                 | Switching vector |   |   |

|------|-------------|-------------------------|-----------------|-----------------|------------------|---|---|

|      | Vecto<br>r  | $V_{ab}$                | V <sub>bc</sub> | V <sub>ca</sub> | A                | В | С |

| 1    | $V_1$       | 1                       | 0               | 0               | 1                | 0 | 0 |

| 2    | $V_2$       | 0                       | 1               | -1              | 1                | 1 | 0 |

| 3    | $V_3$       | -1                      | 1               | 0               | 0                | 1 | 0 |

| 4    | $V_4$       | -1                      | 0               | 1               | 0                | 1 | 1 |

| 5    | $V_5$       | 0                       | -1              | 1               | 0                | 0 | 1 |

| 6    | $V_6$       | 1                       | -1              | 0               | 1                | 0 | 1 |

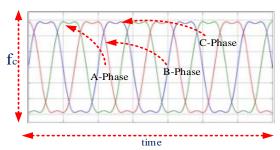

The 3<sup>rd</sup> harmonics elimination based double peak sine reference waveform is used for the reference is used for comparing with carrier waveform.

Phase to Phase Voltage in Fourier,

Phase to Phase Voltage in Fourier,

$$Vab = a_0/2 + \sum_{n=1}^{\infty} (a_n \cos(n\omega t) + b_n \sin(n\omega t)) \quad (10)$$

The V<sub>ab</sub> is voltage between Phase "a" and Phase "b".

$$bn = \frac{4Vs}{n\pi} \sin\left(\frac{n\pi}{2}\right) \sin\left(\frac{n\pi}{3}\right) \quad (11)$$

Due to the quarter wave symmetry along the x-axis, both

$$bn = \frac{4Vs}{n\pi} \sin\left(\frac{n\pi}{2}\right) \sin\left(\frac{n\pi}{3}\right)$$

(11)

a<sub>o</sub> and an are zero. Assuming Symmetry along the y-axis at  $\omega t = \pi/6$ , We can write  $b_n$  as above mentioned.

Phase to Phase Voltage in Three Phase inverter

Vab =

$$\sum_{n=1,3,5}^{\infty} \frac{4Vs}{n\pi} \sin\left(\frac{n\pi}{3}\right) \sin\left(\omega t + \frac{\pi}{6}\right)$$

(12)

Vbc =  $\sum_{n=1,3,5}^{\infty} \frac{4Vs}{n\pi} \sin\left(\frac{n\pi}{3}\right) \sin\left(\omega t - \frac{\pi}{2}\right)$  (13)

Vca =  $\sum_{n=1,3,5}^{\infty} \frac{4Vs}{n\pi} \sin\left(\frac{n\pi}{3}\right) \sin\left(\omega t - \frac{7\pi}{6}\right)$  (14)

$$Vbc = \sum_{n=1,3,5}^{\infty} \frac{4Vs}{n\pi} \sin\left(\frac{n\pi}{3}\right) \sin\left(\omega t - \frac{\pi}{2}\right)$$

(13)

$$Vca = \sum_{n=1,3,5}^{\infty} \frac{^{4Vs}}{^{n\pi}} \sin\left(\frac{n\pi}{^3}\right) \sin\left(\omega t - \frac{7\pi}{^6}\right) \quad (14)$$

Fig. 7 Reference signal for VSI control- Double peak sine waveform

## V. SIMULATION RESULTS AND DISCUSSIONS

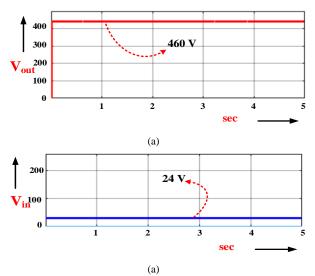

The proposed magnetic coupled DC to DC converter with six switches three-phase VSI for EV drive. The PMSM motor has chosen for EV motor. The table -3, shows the simulation parameter for converter, VSI and PMSM motor. The simulation is developed with MATLAB/Simulink software simulations. The three winding transfer is designed by variable number of winding and inductance values. The converter is designed with 460V DC –link voltage. The battery voltage is considered as 24V to 36V range. The winding ratios  $N_1:N_2:N_3=1:4:8$  at a higher modulation index,  $M_a=0.9$  while maintaining the ST duty ratio at  $D_{ST}=0.236$ .

Table 3. Simulation parameters

| Parameters                             | values        |

|----------------------------------------|---------------|

| Battery voltage, V <sub>B</sub>        | 36V, 2.5KW    |

| Transformer Turns,                     | 1:8:16        |

| $N_1, N_2, N_3$                        |               |

| Power (P)                              | 2 kW          |

| Line to Line voltage (V <sub>L</sub> ) | 400 V         |

| DC-link voltage (VDC)                  | 460V          |

| Frequency (f)                          | 50Hz          |

| F DC-link capacitor.                   | 100MicroF     |

| Stator resistance (Rs)                 | $0.7~\Omega$  |

| Stator inductance (Ls)                 | 0.0047 H      |

| Rotor resistance (Rr)                  | $1.35~\Omega$ |

| Speed                                  | 1300 rpm      |

| ${ m I}_{ m rms}$                      | 5A            |

| $ m V_{rms}$                           | 400V          |

| Torque(T)                              | 8 Nm          |

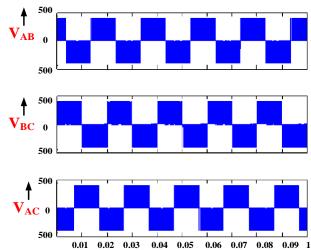

The Fig.8, shows the converter side output voltage for 48V input with BF=6. From the figure, result it could understand that the converter side able to maintain the converter outside voltage ( $V_{\rm DC}$ , DC-link for VSI). The converter able to maintain the 460V. Fig.9 shows the inverter voltage line-voltage. From the results it seen that the VSI is able to give a stater voltage for the drive and giving the suitable voltage for the desired torque –speed. The voltage percentage THD is shown for the line –voltage. From the THD result is it could understand that, the proposed  $3^{\rm rd}$  harmonics is reduced the THD well below.

Fig. 8. Simulation results: Input Battery voltage (  $V_{\rm in}$  ), output voltage (  $V_{\rm DC}$  )

Fig. 9. Simulation results: inverter line – voltage for all three phases  $V_{AB}, V_{BC}, \, V_{CA}$

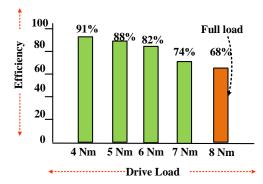

The simulation is extended for calculating the drive performance against different load. The drive load is fixed from 4Nm to 8 Nm, where the 8Nm is a full load case for the test drive. The fig.10 shows the performance chart for drive efferent verses load. During the full load the drive efficiency is observed only 68%. However the efficiency is better during the 4Nm to 6Nm, which is considered as half and ¾ of drive load.

Fig. 10. Simulated drive performance; Efficiency verse different load

# VI. EXPERIMENTAL RESULTS AND DISCUSSIONS

# 1. Experimental Investigation

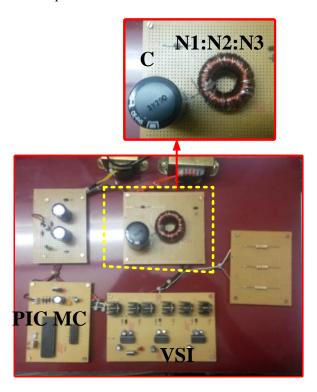

The investigation of the experimental verification for the proposed magnetic coupled DC to DC converter with six-switch three-phase VSI for 200W is developed for R and RL with PIC microcontroller digital implementation collaboration. The PWM is developed in assembly code and implemented in the 3 kHz switching frequency with 6 mircosec dead time. Fig.11.shows the experimental setup of the three-phase VSI connected RL load.

Fig.11.shows the experimental setup of the three-phase VSI connected RL load.

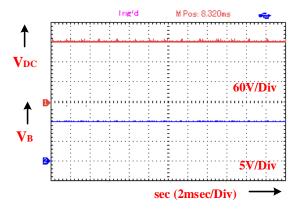

Fig. 13. Simulation results: Input Battery voltage (  $V_B$ ), output voltage (  $V_{DC}$ )

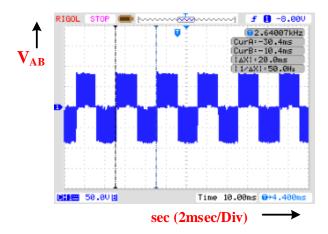

Fig.12. Experimental Line voltage for 0.5 Ma

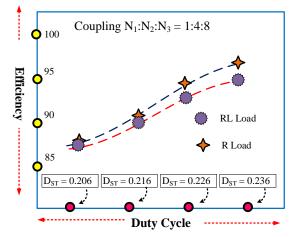

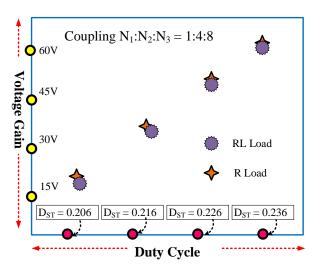

The 100mcroF DC-link capacitor and 10 ohm, 4 mH RL load used to test the converter performance. The TLP250 gate driver circuit is used for six MOSFETs. The voltage and THD waveforms are measured using 2channel DSO. The three winding transfer is designed is for fixed variable number of winding and inductance values to provide a BF=4. The converter is designed with 60V DC – link voltage. The battery voltage is considered as 12V range. Accordingly the ST duty ratio is calculated and fixed as  $D_{ST} = 0.236$  and the winding ratios is designed as  $N_1:N_2:N_3 = 1:4:8$ . During the conditions the inverter is operated with the higher modulation index range 0.5 to 0.9. The Fig.12, shows the converter side output voltage for 12V input with BF=4, and  $D_{ST} = 0.236$ . From the result it could understand that the converter side able to maintain the converter output voltage as 60V ( $V_{DC}$ , DC-link for VSI). Fig.13 shows the inverter voltage line-voltage, V<sub>AB</sub> for M<sub>a</sub>=0.5. The experimental investigation is also verified with R-load and RL-load to compare the converter efficiency. The converter is performing the better range of efficiency between 87 to 96%. The voltage gain of the converter with R and RL load is observed and plotted in Fig.15. From the results, it can see that the converter voltage gain is related to duty cycle and transformer coupling.

Fig. 14. Experimental investigation of converter efficiency. for R-load and RL-load

Fig. 15. Experimental investigation of converter voltage gain for R-load and RL-load

#### VII. CONCLUSION

The proposed magnetic coupled DC to DC converter inverter can yield a high voltage gain (nearly 12 times). The converter voltage gain is related to duty cycle and transformer coupling. Thus, it has more control degrees of freedom in terms its voltage gain comparing with other existing DC to DC converter. The converter studied with six switches three-phase VSI for PMSM based EV drive for its full range of working operation and simulation verification is done through MATLAB/Simulink system software. The laboratory based small scale 200W power circuit is designed and developed and the control algorithm is implemented in PIC microcontroller platform. The analysis, simulation and experimentation validation is confirming the advantages of the converter for EV application.

#### REFERENCES

- C.Bharatiraja, P. Sanjeevikumar, PierluigiSiano, K.Ramesh, and S.Raghu., "Real Time Forecasting of EV Charging Station Scheduling for Smart Energy System", *Energies*, vol. 10, no. 377, pp. 1 to14, March 2017

- 2 J. A. Peças Lopes, F. J. Soares, and P. M. Rocha Almeida, "Integration of electric vehicles in the electric power system," Proc. IEEE, vol. 99, pp. 168–183, Jan. 2011.Do

- 3 Savio A., D.; Juliet, V.; Chokkalingam, B.; Padmanaban, S.; K. Ramachandaramurthy, V. Design and Implementation of a Multiple Charging Point Adapted Hybrid Microgrid Powered Electric Vehicle Charging Station and Its Energy Management Strategy. Preprints 2018, 2018040226 (doi: 10.20944/preprints201804.0226.v1).

- 4 K. Kumar, R. Tiwari, N. R. Babu, S. Padmanaban, M. S. Bhaskar, and V. K. Ramachandaramurthy, "Analysis

- of high voltage-gain hybrid DC-DC power converter with RBFN based MPPT for renewable photovoltaic applications," 2017 IEEE Conference on Energy Conversion (CENCON), Oct. 2017.

- 5 H. Cha, F. Z. Peng, and D. W. Yoo, "Distributed impedance network (Z network) dc-dc converter," IEEE Trans. Power Electron., vol. 25, no. 11, pp. 2722-2733, Nov. 2010.

- 6 Wuhua Li; Xiangning He, "Review of Nonisolated High-Step-Up DC/DC Converters in Photovoltaic Grid-Connected Applications," IEEE Trans. Industrial Electronics, vol.58, pp. 1239–1250, May 2011.

- 7 C.Bharatiraja, S.Jeevananthan., Latha, R., "FPGA based practical implementation of NPC-MLI with SVPWM for an autonomous operation PV system with capacitor balancing", in International Journal of Electrical Power and Energy Systems/ Elsevier, vol. 61, pp.489-509, Oct 2014

- 8 M. Tariq, M. T. Iqbal, M. Meraj, A. Iqbal, A. I. Maswood, and C. Bharatiraja, "Design of a proportional resonant controller for packed U cell 5 level inverter for grid-connected applications," 2016 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Trivendram, kerala, India. 14 -17 Dec 2016.

- 29 C. Bharatiraja, S. Padmanaban, P. Siano, Z. Leonowicz, and A. Iqbal, "A hexagonal hysteresis space vector current controller for single Z-source network multilevel inverter with capacitor balancing," 2017 IEEE International Conference on Environment and Electrical Engineering and 2017 IEEE Industrial and Commercial Power Systems Europe (EEEIC / I&CPS Europe), Milan, Italy,6-9 June 2017.

- 10 P. C. Loh, D. M. Vilathgamuwa, C. J. Gajanayake, Y. R. Lim, and C. W. Teo, "Transient modeling and analysis of pulse-width modulated Z-source inverter," IEEE Trans. Power Electron., vol. 22, no. 2, pp. 498-507, Mar. 2007.

- 11 F. Z. Peng, "Z-source inverter," IEEE Trans. Ind. Applicat., vol. 39, no. 2, pp.04-510, Mar/Apr. 2003.

- 12 H. Cha, F. Z. Peng, and D. W. Yoo, "Distributed impedance network (Z network) dc-dc converter," IEEE Trans. Power Electron., vol. 25, no. 11, pp. 2722-2733, Nov. 2010.

- 13 Y. Tang, S. Xie, and C. Zhang, "Z-source ac-ac converters solving commutation problem," IEEE Trans. Power Electron., vol. 22, no. 6, pp.2146-2154, Nov. 2007.

- 14 P. C. Loh, D. Li, and F. Blaabjerg, "□-Z-source converters," IEEE Trans. Power Electron., vol. 28, no. 11, pp. 4880-4884, Nov. 2013.

- 15 R. Strzelecki, M. Adamowicz, N. Strzelecka, and W. Bury, "New type T-source converter," in Proc. CPE 2009, May 2009, pp. 191-195.

- W. Qian, F. Z. Peng, and H. Cha, "Trans-Z-source converters," IEEE Trans. Power Electron., vol. 26, no. 12, pp. 3453-3463, Dec. 2011.

- 17 M. K. Nguyen, Y. C. Lim, and Y. G. Kim, "TZ-source converters," IEEE Trans. Ind. Electron., vol. 60, no. 12, pp. 5686-5695, Dec. 2013.

- 18 M. Adamowicz, R. Strzelecki, F. Z. Peng, J. Guzinski, and A. H. Rub, "New type LCCT-Z-source converters," in Proc. EPE 2011, Sept. 2011 pp. 1-10.

- 19 M. Adamowicz, J. Guzinski, and P. Stec, "Five-phase EV drive with switched-autotransformer (LCCAt) converter," in Proc. VPPC 2014, Oct. 2014, pp. 1-6.

- 20 Y. P. Siwakoti, P. C. Loh, F. Blaabjerg, S. J. 32 Andreasen, and G. E. Town, "Y-Source impedance network based boost DC/DC converter for distributed generation," IEEE Trans. Ind. Electron., vol. 62, no. 2, Feb. 2015.

- 21 T.K.S Sathayanarayanan, M Ramasamy, C Bharatiraja, JL Munda "Modelling, Impedance Design, and Efficiency Analysis of Battery Assists PV tied Quasi-Z source inverter", in International Journal of Power Electronics and Drive Systems, vol.3, no.7, pp. 816-825, Dec 2016.

- 22 Y. P. Siwakoti, F. Blaabjerg and P. C. Loh, "New magnetically coupled impedance (Z-) Source networks," IEEE Trans. Power Electron., vol. 31, no. 11, pp. 7419-7435, June 2015.

- 23 Y. P. Siwakoti, F. Z. Peng, F. Blaabjerg, P. C. Loh and G. E. Town, "Impedance source network for electric power conversion Part I: A topological review," IEEE Trans. Power Electron., vol. 30, no. 2, pp. 699–716, Feb. 2015.

- 24 C. Bharatiraja and J. L. Munda, "Simplified SVPWM for Z Source T-NPC-MLI including neutral point balancing," 2016 IEEE Symposium on Computer Applications & Industrial Electronics (ISCAIE), Penang, Malaysia, 30-31 May

- 25 Santhakumar, C., Shivakumar, R., Bharatiraja, C., Sanjeevikumar, P. "Carrier shifting algorithms for the mitigation of circulating current in diode clamped MLI fed induction motor drive ", in International Journal of Power Electronics and Drive Systems, vol.8, no.2, pp. 844-852, June 2017

- 26 Y. P. Siwakoti, P. C. Loh, F. Blaabjergand G. Town, "Y-Source Impedance Network," in Proc. APEC 2014, Fort Worth, TX, pp.3362-3366, Mar. 2014

- 27 C.Bharatiraja, S.Raghu, Anathraj, Prabathkumar "Analysis and simulation of magnetically coupled Y shape impedance source inverter", Indian Journal of Science and Technology, Volume 9, Issue 44, pp. 1-7,2016

- 28 C. Bharatiraja, S. Jeevananthan, and J. L. Munda, "A Timing Correction Algorithm-Based Extended SVM for Three-Level Neutral-Point-Clamped MLI in Over Modulation Zone," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 6, no. 1, pp. 233–245, Mar. 2018.

- 29 Y. Tang, S. Xie, and C. Zhang, "An improved Z-source inverter," IEEETrans. Power Electron., vol. 26, no. 12, pp. 3865-3868, Dec. 2011.

- 30 C.Bharatiraja, S. Jeevananthan, S, R. Latha, and V.Mohan, "Vector selection approach-based hexagonal hysteresis space vector current controller for a three

- phase diode clamped MLI with capacitor voltage balancing," IET Power Electronics., vol. 9, no. 7, pp. 1350-1361, June 2016.

- 81 C. Bharatiraja, T. B. Prasad, and R. Latha, "Comparative realization of different SVPWM schemes in linear modulation using FPGA," 2008 IEEE Region 8 International Conference on Computational Technologies in Electrical and Electronics Engineering, Jul. 2008.

- 32 S.Suresh, R.Gnanadass, N.P. Subramaniam, and C.Bharatiraja, "Electric Power Quality Recognition For Distribution Feeders: A Real Time Study", in *Journal* of Electrical Engineering, Vol.17, No.2, pp.51-69, 2017.

- 33 A.Bindu, M.Carolin Mabel, and C.Bharatiraja, "A Real-Time Energy Management Approach And Its Power Converter For PV Powered Plug-In Electric Vehicle", in *Journal of Electrical Engineering*. vol. 17, no.2, 2017, pp.241-247, 2017.

- 34 C. Bharatiraja, R. Latha, "A New Asymmetrical Single Phase 15 Level Reduced Switch Multilevel Voltage Source Inverter", in *Journal of Electrical Engineering*.vol.15, no.4, pp. 1-9, Dec 2015

- 35 P.Ramesh .C.Sharmeela, and C.Bharatiraja, "Nine Level MLI fed Single Phase Induction Motor Drive with Compressor Load Using Artificial Neural Network", in *Journal of Electrical Engineering*, Vol.17, No.2, 2017, pp.242-247, 2017

- 36 P. Anbarasan,S. Ramkumar and C.Bharatiraja,"A Comprehensive Analysis of Carrier Shifting Algorithms for Diode-Clamped MLI Based Drive", in *Journal of Electrical Engineering*, Vol.17, No.2, 2017, pp.52-61, 2017

- 37 C. Bharatiraja, and R. Latha, "A 3 Dimensional Svpwm Algorithm, Its FPGA -Implementation for Multilevel Inverters", in *Journal of Electrical Engineering*, vol.14, Issue 2, Pages 61-70, 2014