# EFFICIENT LOW ENERGY CONSUMPTION OF EMBEDDED SYSTEM BY POSTPONEMENT DPM COMBINED WITH COMPRESSION AWARE DCR

#### Velliangiri. A

Department of Electronics and Communication Engineering, K. S. R. College of Engineering, Tiruchengode, Tamil Nadu, India , velliangiria@gmail.com

#### Periasamy. P. S

Department of Electronics and Communication Engineering, K. S. R. College of Engineering, Tiruchengode, Tamil Nadu, India

Abstract: Low energy consumption, dissipation and fault tolerance area unit typically key objectives within the style of real-time embedded systems. Real-time systems sometimes use system level energy reduction ways Postponement technique supported DPM is employed within which the processors area unit run at the most offer voltage, and might tolerate one transient fault. It will operate with 2 cases with low employment and high employment. Within the case of low employment it's enough to shelve the secondary copy of method to a time when finishing the first process, if the first copy finishes with success, doesn't need corporal punishment any portion of the secondary method. Within the case of high employment, the secondary copy should begin corporal punishment before the first copy finishes, as a result of otherwise if a fault happens throughout the execution of the first copy, there'll be no sufficient time left to execute the secondary copy before the point in time. To fulfill the point in time, the secondary copy are often deferred at the most (D- $\zeta$ ) units of your time once no fault happens, the first copy is dead fully and also the secondary copy is dead for  $(2\zeta-D)$  units of your time. There's no got to execute the remaining  $(D-\zeta)$  of the secondary copy, unless the first copy becomes faulty. During this work, we tend to propose Dynamic Cache Reconfiguration (DCR)exploitation runtime observation of cache parameters to additional improve the energy potency. On merging Postponement technique supported DPM and DCR with leak aware formula is employed which may minimize the general system energy consumption and leak power by considering the temperature. Simulation results show reduction of energy dissipation up to 16% compared to different techniques. The results additionally indicate that for lower set associativity and better task generation, the projected approaches have higher performance

**Keywords**: Postponement DPM, DCR, Energy consumption, fault tolerance.

#### I. Introduction

Energy saving became a vital goal in fashionable embedded systems, particularly for battery operated devices, like autonomous mobile robots and sporting devices, that the diminution of energy consumption ends up in a extended time period, that successively permits saving cash and curb environmental pollution.

Two widely used techniques to save lots of energy within the actual technology area unit Postponement methodology supported Dynamic Power Management (DPM) and Dynamic Cache Reconfiguration (DCR). DPM techniques aim at switch the processor during a low-power inactive state for the longest potential time, therefore suspending the tasks execution as long as potential, still guaranteeing the task period constraints. Dynamic Cache Reconfiguration (DCR) is fantastically effective to downsize vitality use of reserve system.DCR might be seen as a strategy that attempts to get a handle on reserve estimate with various reserve parameters to downsize vitality utilization while not (or with minor) execution corruption. Littler stores contribute less static power anyway may expand reserve misses which may result in broadened dynamic power and execution corruption Therefore, the smallest potential store probably won't be a conceivable goals in a few cases. DCR methods understand the least complex store that coordinates the machine by investigating reserve designs abuse changed plans.

In CMOS technology, that is that the actual leader, power consumption is thanks to each dynamic and static elements, that square measure attributable to the system activity and static dissipation, severally. Unless the system is

off, the static contribution is often gift, severally of the particular performance level. Thus, DCR approaches determined the simplest cache parameters by mistreatment Pareto-optimal point's commerce off energy consumption and performance. Their technique imposes no overhead to the essential path, so cache interval doesn't increase. Whereas DPM solutions square measure best fitted to decreasing the impact of the static part. These techniques can even be integrated to use their complementary options for saving additional energy.

In inserted frameworks, each adaptation to internal failure and low vitality utilization region unit clashing destinations and moreover they're some of the time in refinement to fleeting request needs. Laborious day and age frameworks commonly require equipment excess (replication), anyway the mandatory replication results in a great deal of vitality As of late, analysts have contemplated each adaptation to internal failure and vitality utilization in day and age programming. Here we have considered some vitality the executives systems like Classic DPM, square measure keep running at the most extreme offer voltage and agent recurrence from the earliest starting point of the sum anyway this philosophy doesn't utilize the dynamic voltage scaling ability of processors and Adaptive Hybrid Dynamic Power Management (AH-DPM) calculation is utilized in portable applications and it additionally did not forfeit the normal reaction time of the hard circle, which is still lower than the normal plate get to time indicated in a hard plate particular and power utilization is accomplished by 69.40%.

DCR has as of late attracted obvious interests each universally useful in like manner as day and age frameworks. In day and age frameworks, assortment of strategies exist for utilizing stores viably either by staying away intra-undertaking impedance capriciousness or demonstrating schedulability through reserve mindful transient request examination. Reserve security and store dividing procedures are anticipated for enhance the beyond any doubt thing of the store conduct in past, the key test for utilizing DCR in performing various tasks frameworks is to see once and the best approach to reconfigure the reserve, so vitality utilization is diminished

though every assignment's transient request imperatives are glad. Wang and Mishra connected DCR in delicate era frameworks, amid which undertaking's season of entry and point in time don't appear to be superb in priori, by using static recognizable proof information at runtime for each single dimension store and various dimension reserve chain of command. Ongoing endeavors attempted to blend DCR and DVS along in relentless day and age frameworks. Be that as it may, these methods are either intended for explicit frameworks (e.g., delicate day and age frameworks amid which missing undertaking due dates are bearable) or explicit errand attributes (e.g., intermittent assignments). Also, they're moreover bolstered beyond any doubt suspicions that don't consistently hold, e.g., unimportant or mounted reconfiguration overhead.

From the above examination. diminishing vitality with the constrained deferral have been accomplished by the proposed procedures 1) Postponement dependent on DPM with a spillage mindful calculation is a generally savvy strategy against transient deficiencies and furthermore decreases the spillage control with vitality utilization. Whatever remains of this paper is sorted out as pursues. Segment 2 gives deferment strategy with DPM calculations. Area gives Dynamic Cache Reconfiguration Segment 4 portrays Reliability demonstrate with recreation Results Section 5 depicts the end.

#### **II. Literature Review**

Gilberto Ochoa-Ruiz et.al in 2018 referenced concerning DCS (Distributed Control Systems) show presents awfully explicit issues and requesting needs as far as the idleness, obligation and availability of the of the framework as, it's wide acknowledged that antiquated structures, bolstered PLC (Programmable Logic Controller) models don't appear to be sufficiently compelling for meeting such imperatives, a constraint that comes from the cycle-filter execution of the hidden stages. These impediments are especially clear with the presence of most recent mechanization models, similar to the IEC 61499 typical. some the difficulties visaged by the present modern robotization strategies, as far as the procedural and subject moves that are required for tending to the genuinely necessary dexterous abilities of

future creating frameworks. The IEC 61131-3 ordinary depicted an essential attempt at tending to a few of the issues preventive the appropriation of a regular base for programming for Programmable Logic Controllers, anyway it endures of poor realtime exhibitions and quantifiability issues (particularly in to a great degree dispersed plants), due to the output based nature of the execution stages. The most favorable position of those occasion based execution approaches is that it allows the independent execution of the board forms, while not the worldly request punishments identified with output based computerization frameworks. The occasions alter the execution of interior, client delineated procedures (i.e., the executives calculations) underneath the administration of a unifying administration unit, alluded to as the Execution Control Chart (ECC).

Soheil Aminzadeh and Alireza Ejlali in 2011 correlation four thought about entirely unexpected existing vitality the executives techniques once connected to a recreated challenging timeframe framework. Amid this examination, they require received partner degree logical methodology wherever Markoff models region unit won't to break down the effect of vitality the board procedures on framework dependableness. In the examination, a period application is mapped on a framework that comprises of two indistinguishable process hubs, and technique replication is utilized in order to endure transient mistakes all through strategy execution. Fluctuated researched ways

1. Classic DPM: In this procedure, each the first and auxiliary duplicates of a copied strategy are kept running at the most extreme offer voltage and operational recurrence (Smax) from the earliest starting point of that is all. In various words, this approach doesn't utilize the dynamic voltage scaling capacity of processors anyway rather utilizes the slack time for golf stroke the processors in an extremely hibernation mode to decrease the vitality utilization. This philosophy includes a significant preferred standpoint for debilitating day and age frameworks with abnormal state of reliableness necessities, that is procedure at the most extreme achievable offer voltage winds up in least disappointment rate and therefore least probability of blunder occurrence.

- 2. Classic DVS: This technique proposes to use the DVS capability of methods so as to realize the minimum attainable energy consumption for every process execution.

- 3. Postponement method: In the Postponement system the processors territory unit keep running at the most offer voltage, and that we will endure one transient blame. Subsequently, the dependableness of the Postponement procedure is that equivalent to that of the great DPM.

- 4. Hybrid method: In this procedure the primary duplicate of the technique is kept running at a diminished offer voltage and in this way the optional duplicate is conceded and furthermore dead at a diminished offer voltage. Here, picking the accessibility voltages of the first and optional duplicates, and picking the best time for starting the auxiliary duplicate should be done thoroughly to acknowledge most vitality sparing.

Primary commitment of this paper is four extraordinary examination totally procedures utilized for decreasing the vitality utilization of repeated blame tolerant debilitating period frameworks, and proposing assortment of style tips, all together that a creator will choose that vitality the board system is appropriate for a given application. The sole burden is required to support the present procedures and to coordinate the enhanced and unique methodologies diagnostically. On the off chance that the framework utilizes heterogeneous process parts as opposed to indistinguishable processors, it will prompt higher adaptation to internal failure.

Shounak Chakraborty et.al in 2011 lessened static power utilization progressively development down or turning on store banks dependent on upon framework execution and reserve bank use measurements. Development down of a reserve bank remaps its future solicitations to an alternate dynamic bank, alluded to as target bank. The arranged strategy is assessed on 3 totally extraordinary usage strategies, viz (1) The framework can choose to shutdown or turn-on some store banks procedure intermittently all through the execution. (2) The framework permits to shutdown banks at first and once the bank restarting starts, no more shutdowns is allowed further. (3) This approach resizes reserve like first strategy with some predefined time cuts, inside which store can't be resized. Relate degree prior work to downsize store estimate by move down reserve banks until an admissible debasement edge in IPC. This strategy is talked as BSP. Notwithstanding, this strategy can't give satisfactory store house to the technique just on the off chance that it needs extra reserve house in future, all through execution. The present work master represents a dynamic reserve institutionalization strategy that considers execution and region of reference as its requirements for dealing with the store estimate.

In this analyses, they require utilized a sixteen center secured CMP plan, wherever every tile contains a processor center with an individual L1 store, and a cut of shared L2 reserve, alluded to as L2 store bank. These arrangement of tiles territory unit interconnected with each other during a time organize work. Each tile contains a switch in it for act among the tiles. This proposition taught store bank end to spare loads of intensity and stimulant to amend IPC debasement. to measure this approach, tests region unit performed on 3 very surprising strategy arrangements. Those territory unit strategy setup allows the banks on/off methodology to proceed all through the technique execution with a reconfiguration interim of 2M clock-cycles, bank stimulant is admissible to help the IPC and Cache needs revision over the strategy execution.

Hadi Hajimira et.all in 2012 manages the difficulties and related open doors in reconciliation dynamic store reconfiguration with code pressure to hold the advantages of each methodology. They created prudent heuristics to investigate enormous region of twolevel reserve pecking order in order to check the aftereffect of a two-level store on vitality utilization and demonstrated that code pressure that significantly lessens the code size may likewise encourage the store reconfiguration method to settle on similarly littler store sizes, littler cooperatively, or littler line estimate while execution debasement, accordingly, diminishes store vitality utilization impressively.

Structure of temperate pressure systems needs to mull over 2 indispensable perspectives. In the first place, the compacted code must help the shot of starting the decompression all through execution at numerous focuses inside the program (i.e., branch targets). Second, since decompression is performed on-line, all through

program execution, decompression calculations should be snappy and control temperate to accomplish investment funds in memory size and power, while not trading off execution. We will in general investigate differed pressure procedures (counting lexicon based pressure, bitmask-based pressure and Huffman coding) that speak to an exchange off between pressure execution and decompression overhead. It's normal that by pressure headings the store conduct of projects isn't any more extended steady. Consequently to possess the ideal store arrangement, a great deal of examination should be done and in addition hit/miss conduct of the packed projects. This framework utilizes an ideal blend of code pressure and dynamic institutionalization of two-level reserve parameters with minor or no effect on worldly course of action requirements. Our trial results incontestable 61% decrease on the normal in by and large vitality utilization of the reserve plot also as up to 75% execution enhancement (contrasted with DCR just) in installed frameworks.

Weixun Wang et.al in 2011 arranged a general and adaptable algorithmic program for vitality enhancement bolstered dynamic reconfiguration in performing various tasks frameworks and built up a general algorithmic program that exhaustively tackles vitality mindful reconfiguration issues in uniprocessor performing multiple tasks frameworks. This algorithmic program is adaptably parameterized and may be acclimated offer tradeoffs between era and goals quality. The most finish of this paper is abridged

- a) The algorithmic program expect that each undertaking are regularly dead beneath one or numerous designs and finds the ideal arrangement task to decrease vitality utilization though ensuring all the time limitations. each setup may compare to somewhere around one reserve arrangement, one voltage level or a blend of them. so the algorithmic program will it is possible that one by one or in the meantime suit DCR and DVS methods.

- b) It licenses money related estimation of move from one setup to an alternate. Therefore, it's endowments over existing procedures that it will viably think about factor runtime overhead.

c) The calculation can be adaptably parameterized to tradeoff between calculation running time and arrangement quality. Our trial results demonstrate that the running time can be definitely diminished while just minor quality corruption is watched.

The advantages territory unit first, it will cause a great deal of vitality investment funds than between undertaking way DVS/DCR procedures. Besides, it will adequately bring variable reconfiguration overhead into thought. At long last, this algorithmic program are regularly adaptably parameterized all together that exclusively slight goals quality debasement are frequently recorded for definitely lessened day and age request. it's conjointly independent of errand qualities and programming approach.

#### III. Proposed Methodology

In this technique, both the essential and auxiliary duplicates of a copied procedure are kept running at the most extreme supply voltage and operational recurrence (Smax) from the beginning of the period. At the end of the day, this technique does not utilize the dynamic voltage scaling ability of processors however rather utilizes the slack time for putting the processors in a hibernation mode to lessen the vitality utilization.

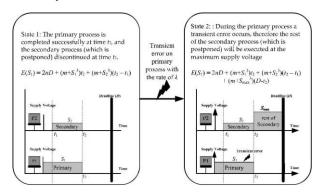

**Fig.1.** The abstraction of Markov model of a system where one process is replicated for tolerating one transient fault and process postponement with voltage scaling are used to conserve energy.

This strategy has a profitable favorable position for hard ongoing frameworks with abnormal state of unwavering quality prerequisites, that is handling at the most extreme conceivable supply voltage results in

least disappointment rate and subsequently least likelihood of blunder event [6], [7].

As appeared in Fig. 1, when both the duplicates of the procedure begin running at the most extreme supply voltage toward the beginning of the period, they will complete in the meantime, after  $\tau$  units of time. Until the start of the following time frame, both the processors can be placed in the hibernation mode. At the end of the day, every processor works for  $\tau$  units of time and moves toward becoming slept for the rest of the  $D-\tau$  units of time.

Here, we don't have to utilize the Markov model to compute the vitality utilization. Since both the essential and auxiliary duplicates begin in the meantime and keep running at the greatest supply voltage, the aggregate vitality utilization is just multiple times the vitality of (2) (with S =Smax)

$$E = 2[Phib . D + (Psi + \Psi . S^3 max)\tau]$$

-----(1)

where D is the deadline or the length of the period. Also the system reliability is [8], [9]

$$R = 1 - (1-e^{-\hbar 0\tau})^2$$

-----(2)

where &0 is the failure rate when supply voltage and operational frequency set to Smax.

#### 3.1 Postponement Method

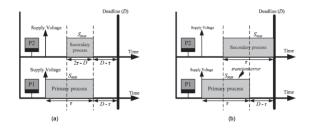

**Fig.2.** Postponement method (a) Primary process finishes successfully (b) Transistor error occurs during the execution of primary process.

In this strategy, which is first proposed by Unsal et al. [10], the imitated (optional) duplicate of a procedure is delayed, trusting that the essential procedure will complete effectively and the framework won't require finishing the recreated duplicate. In this technique, neither the essential nor the repeated duplicate use voltage scaling and them two are kept running at the most extreme supply voltage. Fig. 2 outlines this strategy. Fig. 2a demonstrates the situation where the essential procedure completes effectively, and thus it is conceivable to dispose of the rest of the piece of the optional procedure directly subsequent to completing the essential one. Fig. 2b demonstrates the situation where the auxiliary procedure ought to be finished before the due date as a transient blame has happened amid the execution of the essential procedure.

Like the great DPM strategy, in the Postponement technique the processors are kept running at the most extreme supply voltage, and can endure one transient blame. dependability Subsequently, the the of Postponement technique is equivalent to that of the exemplary DPM and is given by (11). To break down the vitality utilization of the Postponement technique, we have to think about the accompanying cases as for the framework remaining task at hand (i.e.,  $L = \tau/D$ ). It ought to be noticed that progressively frameworks, we have  $0 \le L \le 1$ .

(Case A)  $L \leq 1/2$ : (low outstanding task at hand). For this situation, the outstanding task at hand is low enough to defer the auxiliary (reproduced) duplicate of the procedure to a period in the wake of completing the essential procedure. This implies, in a time of the application, if the essential duplicate completes effectively, we don't require executing any bit of the optional procedure. Nonetheless, if the essential duplicate of the procedure falls flat, the auxiliary duplicate must be executed totally. For this situation, utilizing the Markov display procedure we can acquire that the normal vitality utilization is

$$E = 2Phib . D + (Psi + \Psi . S^3 max)\tau + \Lambda_0 (Psi + \Psi . S^3 max)\tau -----(3)$$

(Case B)  $L \geq 1/2$ : (high remaining task at hand). For this situation the second-exhibit duplicate must begin executing before the essential duplicate completions, in light of the fact that generally if a blame happens amid the execution of the essential duplicate, there will be no adequate time left to execute the optional duplicate before the due date. To meet the due date, the auxiliary duplicate can be deferred at most  $(D-\tau)$  units of time. Thusly, as appeared

in Fig. 2a, when no blame occurs, the essential duplicate is executed totally and the optional duplicate is executed for  $(2\tau\text{-}D)$  units of time. There is no compelling reason to execute the rest of the  $(D-\tau)$  of the optional duplicate, except if the essential duplicate ends up flawed. For this situation, utilizing the Markov show method ,we can get that the normal vitality utilization is

E = 2Phib . D + (Psi + Ψ . S<sup>3</sup> max )τ +(Psi + Ψ . S<sup>3</sup> max ) (2τ-D) +

$$\Lambda_0$$

(Psi + Ψ . S<sup>3</sup> max ) (D-τ)

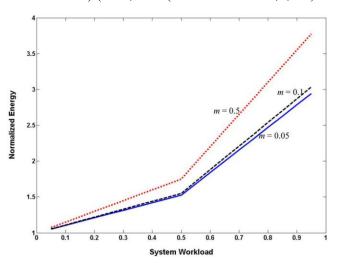

**Fig.3.**Postponement method energy consumption versus system workload.

An outline which demonstrates the vitality utilization of the Postponement technique versus the framework outstanding task at hand is portrayed in Fig. 3. In this outline standardization is utilized, which implies that the due date and the most extreme exchanging power are thought to be 1. Both the components m and n are shifts somewhere in the range of 0.1 and 0.5. Not surprisingly, the incline of the bend changes when the framework remaining burden passes the esteem 0.5.

# 3.2 Dynamic Cache Reconfiguration method with leakage aware algorithm:

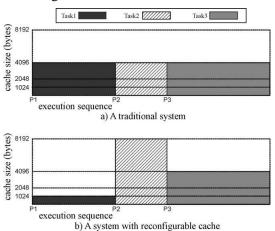

In power constrained installed frameworks, almost 1/2 the general power utilization is ascribed to the store framework Γ121. **Applications** require enormously totally extraordinary reserve needs as far as store measure. line size, and associativity. Examination demonstrates that practicing the store to application's wants will significantly curtail vitality utilization [13]. Fig. four delineates anyway vitality utilization is

decreased by exploitation between undertaking (application-based) store reconfiguration in an exceedingly direct framework supporting 3 In application-based reserve assignments. institutionalization, DCR happens once an errand begins its execution or it resumes from partner intrude (either by acquisition or once execution of another undertaking finishes) and furthermore a similar store for the machine gets picked in spite of if it's going from the begin or continuing wherever in the middle. 4 a)depicts a regular framework and 4(b) portrays a framework with a reconfigurable store. For the comfort of outline we should expect store estimate is that the exclusively reconfigurable parameter of reserve (associativity and line measure are overlooked). Amid this model, Task1 begins its execution at time P1.

Fig. 4. DCR for a system with three tasks.

Task2 and Task3 start at P2 and P3 severally. In an exceedingly old methodology, the framework perpetually executes utilizing a 4096-byte store. We tend to choice this reserve as base store all through the paper. Base store is that the most perfectly awesome reserve setup advanced for every one of the errands. With the decision of reconfigurable store, Task1, Task2, and Task3 execute exploitation 1024-byte reserve starting at P1, 8192-byte store starting at P2, and 4096-byte store starting at P3 severally. Through right decision of store measure for each undertaking the framework can do critical amount of vitality reserve funds likewise as performance gains compared to using only the base cache.

The between undertaking DCR issue is characterized as pursues. Think about an arrangement of n applications (errands)  $A = \{a1, a2, a3, \ldots, an\}$  proposed to keep running on a

configurable reserve design equipped for supporting m conceivable store arrangements  $C = \{c1, c2, c3, \ldots, cm\}$ . We characterize e(cj, ai) as the aggregate vitality devoured by running application ai on the engineering with reserve arrangement cj. We additionally characterize  $co \in C$  as the ideal reserve design for application ai, to such an extent that  $e(co, ai) \le e(cj, ai)$ ,  $\forall cj \in C$ . Through thorough investigation of every single conceivable design of  $C = \{c1, c2, c3, \ldots, cm\}$ , best vitality ideal reserve design for every application can be found.

Dynamic reserve reconfiguration has been widely contemplated in numerous works [14–17]. The reconfigurable store plan professional presented by Zhang et al. [15] decides the best reserve parameters by exploitation Pareto-ideal focuses mercantilism off vitality utilization and execution. Their strategy forces no overhead to the imperative way, so reserve time interim doesn't increment. Chen et al. [18] presented a totally one of a kind reconfiguration the executives equation to quickly look through the enormous style zone of potential reserve setups for the best one. None of those methodologies consider the results of compacted code on store reconfiguration.

DCR is seen as a technique that endeavors to press store measure with elective reserve parameters to downsize vitality utilization while not (or with minor) execution debasement. Littler reserves contribute less static power anyway may build store misses which may result in swelled unique power and execution corruption (longer execution time so higher vitality utilization). Consequently, the most modest potential reserve probably won't be a conceivable answer in a few cases. DCR methods understand the best reserve that coordinates the machine by investigating store designs exploitation fluctuated plans. Amid this paper, we tend to demonstrate that code pressure that extensively decreases the code size may likewise encourage the reserve reconfiguration strategy to choose similarly littler store sizes. littler associativity, or littler line estimate while not execution corruption, along these lines, lessens reserve vitality utilization impressively.

The configurable reserves utilized in our work are bolstered the structure outlined in [19]. The hidden reserve configuration contains four separate banks that may work as four separate

manners by which. Uncommon setup registers are acclimated educate the reserve tuner a custom equipment or a light-weight technique – to connect manners by which determined the associativity is modified. The exceptional registers may likewise be intended to quit working manners by which to change the store measure. Also, by designing the get unit to get reserve lines in changed lengths, we can adjust the street sizes. The world overhead for this plan is 3%. Also, looking a middle of 5.4 setups to search out the best design includes a frightfully low vitality utilization of 11.9 Garden State on the normal. This vitality is irrelevant contrasted with the vitality utilization in seat denotes that is a 2.34 J on the normal. Amid this paper the sole a large portion of that we tend to utilize is dynamic store reconfiguration. It implies that our plan isn't self-tuning and has a great deal of less overhead contrasted with [19]

## 3.3 Compression-aware DCR

Here, we tend to consider frameworks with one dimension reserve. We tend to broaden our methodology for frameworks with two-level store. Calculation 1 traces the primary strides in our store arrangement decision inside the nearness of packed applications. The equation gathers reproduction results for all potential store arrangements (reserve sizes of 1KB, 2 KB, 4 KB, and 8 KB; associativity of 1, 2, 4-way; store line sizes of 16, 32, 64). It finds the best vitality best reserve arrangement for each application through entire investigation of all potential store setups of  $C = \{c1, c2, c3, \ldots, cm\}$ }. scope of reproduction cycles for each run is gathered bolstered the reenactment results. The vitality model of [15] is utilized to compute the vitality utilization exploitation the store hit and miss measurements. The recipe at last develops the humanist best options and returns it in an exceedingly list. The principal vitality prudent reserve setup among all humanist best choices that fulfills transient plan needs of the apparatus is picked straightaway. Assume there are 2 store arrangements, C1 with execution time of 2 million cycles and vitality utilization of 5 mJ and C2 with execution time of 1.8 million cycles and vitality utilization of 6 mJ, out there inside the humanist best rundown of choices. In the event that the errand ought to be wiped out 1.9 million cycles, the snappier extraordinary (C2) gets picked. On the off chance that the worldly course of action request of the errand isn't constrained by 2 million cycles, the extra vitality efficient reserve unique (C1) gets tip top.

The calculation is similar to old DCR anyway utilizes compacted code. So the recreation/profiling framework must have decompression unit to supply the intensity of mystery composing com-squeezed bearings. For example, for our situation, we tend to uphold and set the ideal decompression schedules/capacities for individual pressure calculations in clear scalar test system.

In this segment, we tend to consider frameworks with only one dimension of reconfigurable reserve engineering; so scope of store con-figurations is small. In this manner we can altogether investigate every single potential arrangement in an exceedingly reasonable time. Since the reconfiguration of associativity is accomplished by methodology connection, 1 KB L1 store will exclusively be immediate mapped as elective 3 banks are quit working. For a comparable reason, 2KB store will exclusively be intended to coordinate mapped or 2-way associativity.

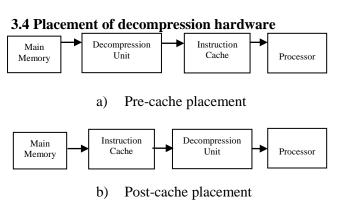

Fig 5: Different placement of decompression unit.

Fig. 5 demonstrates 2 totally unique position of the decompression unit. In pre-store position the memory contains packed code and headings are hang on in reserve in unique kind. Though, inside the post-reserve position the decompression unit is put among store and processor so every memory and reserve contain com-squeezed directions.

Our investigations demonstrate that having the pre-reserve position has next to zero effect on vitality and execution of store. Amid

this case uncompressed headings are hang on inside the reserve and once store miss occurs, the store controller requests that the decompression unit supply a square of bearings. In larger part of the cases the decompression equipment needs one check cycle in pipelined mode (as appeared in 5), subsequently one clock cycle will be valuable to the dormancy of whole square bring. In uncommon cases, e.g., when the essential guidance of the square isn't compacted, it'll present 2 cycle punishment since it'll take 2 cycles to get and decompress the guidance [20].

Consolidating pressure, reserve miss punishment caused by heart get dormancy is decreased inferable from enhanced data measure (since compacted code is littler). Moreover, offchip get to vitality (the transports to primary memory and memory get to) is also lessened since the decompression motor peruses packed code from memory prompting lower movement to principle memory. In any case, post-reserve arrangement will acquaint essential execution overhead with the framework. Seong and Mishra [21] presented a bitmask-based pressure method that adds no punishment to the framework execution exploitation pipelined one-cycle decompression motor with unimportant power request.

With regards to installed frameworks one in everything about most objectives is expanding vitality investment funds while ensuring the framework can address applications issues. Generally, choosing a reserve arrangement for vitality investment funds may end in execution corruption. How-ever, the synergistic mix of store reconfiguration and code pressure permits vitality reserve funds while not loss of execution. Our anticipated procedure gives relate temperate and best methodology for store institutionalization upheld static recognizable proof exploitation compacted programs.

#### 3.5 Tuning of two-level caches

In this area, we tend to think about the effect of a two-level store pecking order on pressure and DCR. We tend to consider a framework with a brought together (guidance/information) level 2 store (L2). We tend to pack exclusively headings. In elective words, we tend to don't consider data pressure amid this paper. In any case, picking vitality

temperate reserve design for L2 store relies upon each dimension one guidance and data stores (IL1 and DL1). So we tend to consider the vitality utilization of the total reserve framework together with IL1, DL1, and L2.

We blessing temperate heuristics to think of profile tables with productive store designs. Institutionalization a two-level reserve faces the issue of investigating a huge design territory. Amid this paper, we tend to inspect average investigation parameters of a two-level store in regular implanted frameworks. As referenced amid this past Section, there are 18 (=3 + 6 + 9) design contender for L1 reserves. Let Sil1 and Sdl1 mean the size of investigation territory for IL1 store and DL1 reserves, severally. Along these lines we've Sil1 = 18 and Sdl1 = 18. For L2 reserve, we pick 8 KB, 16 KB and 32 KB as store sizes; 32, 64 and 128 bytes as line sizes; 4-, 8-and 16-way set associativity with a 32 KB store design made out of four separate banks. So also, there are 18 conceivable arrangements (Sul2 = 18). For correlation, we have picked a base store pecking order, which mirrors a worldwide ideal arrangement for every one of the undertakings, comprising of two 2 KB, 2-way set affiliated L1 reserves with a 32 byte line estimate, and a 16 KB, 8-way set cooperative bound together L2 store with a 64 byte line measure. The rest of this area portrays our proposed investigation methods.

#### 3.6 Exhaustive exploration

Naturally, if the 2 dimensions of reserves is investigated severally, one will basically profile one dimension at any given moment though holding the contrary dimension to a run of the mill design, which can end in a way littler investigation region. In any case, there's no assurance that the blend of 3 severally discovered vitality ideal designs would be going to the world best one. The 2 store levels affect each other's conduct in shifted manners by which. For instance, L2 store's setup decides the miss punishment of the L1 reserves. Additionally, the amount of L2 store gets to specifically relies upon the amount of L1 reserve misses.

The undeniable because of understand the best setup is to look the entire zone completely. Since the guidance and data stores may have totally extraordinary designs, there are 324 (=Sil1\*Sdl1) potential arrangements for L1 reserve. Expansion of the L2 store will build the arranging territory size to 4752 (Not sufficient Sil1\*Sdl1\*Sul2 because of the hopefuls amid which L2 reserve's line estimate is littler than any of the L1 stores are disposed of). We tend to utilize the entire procedure for examination with the heuristics gave inside the accompanying areas. Style of those heuristics is propelled by the investigation heuristics of Wang and Mishra [22]. Be that as it may, our methodology furthermore thinks about the effect of pressure all through investigation.

#### 3.7 Independent L1 cache tuning – ICT

While totally unique store levels are dependent on each other, our underlying outcomes exhibit that guidance and data reserves independent. relatively Amid examination, we tend to settle one's design though unique the other's to inspect regardless of whether variable one effects the secured one. We tend to see that the distinguishing proof measurements for the guidance store for all intents and purposes remain indistinguishable with totally unique data reserves and the a different way. It's in the primary due to the specific actuality that get to example of L1 store is just dictated by the application's attributes, and furthermore the guidance and data streams are similarly independent from each other. In addition, factors moving the guidance reserve's vitality utilization moreover as execution, (for example, hit vitality, miss vitality and miss punishment cycles) have almost no reliance on the data store and the a different way.

This perception offers an opportunity to downsize the investigation territory. We tend to propose **ICT** independent institutionalization heuristic - all through that IL1 and DL1 reserves perpetually utilize a comparative design while investigating with all L2 store setups. This procedure prompts an entire of 288 arrangements - a significant hamper of the underlying sum, however' still not little. All through the static examination, we tend to fabricate accounting together with the vitality utilizations and miss cycles of each reserve separately. The vitality ideal IL1 store is that the one with the base vitality utilization of itself (and same for DL1 reserve and L2 reserve). We choose the reserve setup mix made out of the 3 locally vitality ideal stores in light of the fact

that the vitality ideal reserve chain of command to be hang on inside the profile table.

#### 3.8 Interlaced tuning – ILT

We adjust the technique utilized in TCaT [2] and propose ILT – reticulate institutionalization heuristic – that discovers vitality ideal parameters all through the investigation. The basic arrangement is to tune reserve parameters inside the request of their significance to the general vitality utilization, that is store estimate pursued by line measure and finally associativity. To broaden the probabilities of discovering best L2 reserve measure, that we tend to accept has the best significance, we tend to blend the investigation of L2 store's size and associativity along. ILT is depicted underneath:

- 1. First, tune by store estimate. Hold the IL1's line estimate, associativity in like manner as DL1 to the most diminutive design. L2 is prepared to the base reserve. Investigate every one of the 3 guidance store sizes (1 KB, 2 KB and 4 KB) and decide the vitality ideal one(s). Perform same investigations for DL1 store measure. In L2 measure investigation, we tend to endeavor all the associativities for each reserve estimate. We tend to set L1 sizes to the vitality ideal ones inside the strategy for discovering vitality ideal L2 size(s).

- 2. Next, tune by line estimate. We tend to set reserve sizes to the vitality ideal ones and L2's associativity found inside the activity in investigating vitality ideal line sizes for each store. These 2 undertakings are lasting for each L1 reserves and L2.

At long last, tune by associativity. We tend to set the reserve sizes and line sizes to the vitality ideal ones in investigating vitality ideal associativity. Note that we tend to exclusively investigate associativities for L1 stores amid this progression. All through the technique for discovering DL1's best associativities, we tend to have just got all the contrary parameters we needed to reason the full quantities of execution cycles that are required inside the profile table.

In the worst case, ILT explores thirty configurations. The primary step explores half dozen for L1 caches and 9 for L2 cache. The second step explores 9 (=3\*3) candidates. Final

step explores 6 (=3\*2) candidates. However, in most cases, there are plenty of repetitive configurations throughout the method that we have a tendency to solely need to execute once. In apply, ILT has exploration area size of around 19 configurations.

#### 3.9 Hierarchy level independent tuning – HIT

In spite of the fact that we tend to proclaim that IL1 and DL1 is world class severally, now and again it's higher to investigate the 2 level one reserves along. Assume for an explicit benchmark, there's an outsized variety inside the need L2 measure for information/guidance once unique IL1 or DL1. Amid this case, utilizing a monster segment of L2 for guidance for a specific IL1 arrangement will affect DL1 in a roundabout way (may expand data get to miss quantitative connection in L2). Since ICT discovers vitality ideal reserves for IL1 and DL1 severally while not considering the effect of each on L2 store conduct, it will turn out problematic outcomes. we tend to professional posture HIT – Hierarchy Level independent institutionalization - amid which we tend to first understand the best store arrangements for level one reserves settling L2 to the base store. We tend to investigate all potential 324 (=18\*18) blends for IL1 and DL1 reserves and pick the vitality best ones. Next we tend to settle L1 reserves to the discovered vitality best stores inside the activity and investigate every one of the 18 possibility for L2 store. In synopsis, ILT investigates exclusively 30 setups, though ICT and HIT investigate 288 and 342 (=324 + 18) arrangements, severally.

### IV. Experiments

So as to evaluate pressure mindful store design tradeoffs, we've connected philosophy to pick inserted framework benchmarks. Following a comparative stream in past Sections we tend to first research reconciliation of code pressure with DCR for frameworks with one dimension of reserve. In segment zero, we tend to stretch out our investigations to guage our procedure with the nearness of a two-level store.

#### 4.1 Experimental setup

We inspected cjpeg, djpeg, epic, and adpcm (rawcaudio), g.721 (encode, unravel)

benchmarks from the MediaBench [19] and dijkstra, patricia from MiBench [20] incorporated for the Alpha target structure. These benchmarks ar all extraordinarily intended for installed frameworks and fitting for the store setup parameters. All applications were dead with the default input sets provided with the benchmarks suites.

extraordinary Three totally code pressure methods together with bitmask-based, word reference based and Huffman code pressure were utilized. To accomplish the best gettable pressure proportions, in bitmask-based pressure, for each application we tend to analyzed word references of 1 KB, 2 KB, 4 KB, and 8 KB. Relatively like Seong and Mishra [13] we tend to attempted 3 cover sets together with one 2-bit slippy, 1-bit slippy and 2-bit affixed, and 1-bit slippy and 2-bit secured veils. similarly for word reference based and Huffman pressure we tend to utilized zero.5 KB, 1 KB, 2 KB, 4 KB. 8 KB vocabulary sizes with 8 bits, sixteen bits and thirty two bits word sizes. We tend to got wind that dictionary size of two PC memory unit and word size of sixteen bits are the best choices for this arrangement of benchmarks. The basis is that exploitation eight bits words will expand the amount of pressure call bits and exploitation thirty two bits word estimate diminishes the words frequencies impressively. Henceforth, as recreation results appeared, sixteen bits word measure is that the best choice.

**Fig.6**. Energy consumption of selected minimal-energy cache normalized to base cache.

We utilized the configurable reserve configuration created by Zhang et al. [15] with a four-bank store of base size 4 KB, that offers sizes of 1 KB, 2 KB, and 4 KB, line sizes beginning from 16 bytes to 64 bytes, and associativity of 1-way, 2-way, and 4-way. For examination capacities, we tend to utilized the base store arrangement for L1 set to be a four

PC memory unit, 4-way set affiliated reserve with a 32-byte line measure, a genuinely regular setup that meets the normal wants of the contemplated benchmarks.

To get store hit and miss insights, we tend to change the simple Scalar toolset [25] to modify and recreate packed applications. We tend to authorized and set the ideal decompression schedules/capacities individual pressure calculations in clear scalar machine. We tend to considered the inactivity of decompression unit thoroughly. Decompression unit will decompress resulting guidance in one cycle (in pipelined mode) on the off chance that it finds the total required bits in its support. Else, it takes one cycle (or extra cycles, if store miss happens) to get the required bits into its cradle and on extra cycle to decompress resulting guidance. Accuracy of the pressure and decompression calculations was confirmed by examination the yields of packed applications with uncompressed adaptations. The execution of decompression overhead incorporates decompression unit cushion flush overhead as a result of hops, and variable inertness of memory peruses in each square get (in view of variable length compacted code). These overhead are irrelevant reliable with the test results.

We connected a comparative vitality show utilized in [26], that ascertains every powerful and static vitality utilization, memory dormancy, PC equipment slow down vitality, and primary memory bring vitality. The vitality show was changed to join decompression vitality. We tend to refresh the dynamic vitality utilization for each reserve setup exploitation CACTI four.2 [27].

#### V. Conclusion

Streamlining procedures are generally utilized in implanted frameworks to enhance by and large territory, vitality and execution necessities. Dynamic store reconfiguration (DCR) and DPM is extremely viable to diminish vitality utilization of implanted framework. Code pressure in DCR can altogether lessen memory prerequisites, and may enhance execution in numerous situations. In this paper, we displayed a synergistic mix of DCR and code pressure with delay DPM for installed frameworks. Our system utilizes a perfect mix of code pressure and delay DPM with minor or no

effect on timing imperatives. Our test results showed 67% decrease all things considered in general vitality utilization of the store subsystem and up to 80% execution enhancement (contrasted with DCR just) in implanted frameworks.

#### VI. References

- [1] Soheil Aminzadeh and Alireza Ejlali, A Comparative Study of System-Level Energy Management Methods forFault-Tolerant Hard Real-Time Systems in IEEE TRANSACTIONS ON COMPUTERS, VOL. 60, NO. 9, SEP 2011.

- [2] Hadi Hajimiri , Kamran Rahmani, Prabhat Mishra, Compression-aware dynamic cache reconfiguration for embedded systems in Elsevier Sustainable Computing: Informatics and Systems 2 (2012).

- [3] Gilberto Ochoa-Ruiz, Lina Maria Aguilar-Lobo et.al , Towards Dynamically Reconfigurable SoCs (DRSoCs) in industrial automation: State of the art, challenges and opportunities in Elsevier Microprocessors and Microsystems 62 (2018).

- [4] Shounak Chakraborty , Hemangee K. Kapoor, Performance linked dynamic cache tuning: A static energy reduction approach in tiled CMPs in Elsevier Microprocessors and Microsystems 52 (2017).

- [5] Weixun Wang, Sanjay Ranka, Prabhat Mishra, Energy-aware dynamic reconfiguration algorithms for real-time multitasking systems in Elsevier Sustainable Computing: Informatics and Systems 1(2011).

- [6] A. Ejlali, B.M. Al-Hashimi, M.T. Schmitz, P. Rosinger, and S.G. Miremadi, "Combined Time and Information Redundancy for SEU-Tolerance in Energy-Efficient Real-Time Systems," IEEE Trans. Very Large Scale Integration Systems, vol. 14, no. 4, pp. 323-335, Apr. 2006.

- [7] D. Zhu, R. Melhem, and D. Moose, "The Effects of Energy Management on Reliability in Real-Time Embedded Systems," Proc. Int'l Conf. Computer Aided Design (ICCAD '04), pp. 35-40, Nov. 2004.

- [8] Fault-Tolerant Computer System Design, D.K. Pradhan, ed. Prentice- Hall, 1996.

- [9] B.W. Johnson, The Design and Analysis of Fault Tolerant Digital Systems. Addison-Wesley, 1989.

- [10]O.S. Unsal, I. Koren, and C.M. Krishna, "Towards Energy Aware Software-Based Fault-Tolerance in Real-Time Systems," Proc. Int'l Symp.

- Low Power Electronics Design (ISLPED '02), pp. 124-129, Aug. 2002.

- [11] H. Kopetz, Real-Time Systems: Design Principles for Distributed Embedded Applications. Kluwer Academic Publishers, 2002.

- [12] A. Malik, B. Moyer, D. Cermak, A low power unified cache architecture providing power and performance flexibility, ISLPED (2000).

- [13]A. Gordon-Ross, F. Vahid, N. Dutt, Automatic tuning of two-level caches to embedded applications, DATE (2004).

- [14] A. Gordon-Ross, F. Vahid, N. Dutt, Fast configurable-cache tuning with a unified second level cache, in: International Symposium on Low Power Electronics and Design, 2005.

- [15]C. Zhang, F. Vahid, W. Najjar, A highly-configurable cache architecture for embedded systems, in: 30th Annual International Symposium on Computer Architecture, June 2003.

- [16] P. Vita, Configurable Cache Subsetting for Fast Cache Tuning, in: Design Automation Conference, DAC, 2006.

- [17] D.H.Albonsi, Selective Cache Ways: On-Demand Cache Resource Allocation, 2000.

- [18]L. Chen, X. Zou, J. Lei, Z. Liu, Dynamically reconfigurable cache for low-power embedded system, in: Third International Conference on Natural Computation, 2007.

- [19] C. Zhang, F. Vahid, R. Lysecky, A self-tuning Cache Architecture for Embedded Systems, DATE (2004).

- [20]C. Murthy, P. Mishra, Lossless Compression Using Efficient Encoding of Bitmasks, IEEE Computer Society Annual Symposium on VLSI, 2009, pp. 163–168.

- [21]S. Seong, P. Mishra, Bitmask-based code compression for embedded systems, IEEE Trans. CAD (2008) 673–685.

- [22] W. Wang, P. Mishra, Dynamic reconfiguration of two-level caches in soft realtime embedded systems, in: IEEE International Symposium on VLSI, 2009.

- [23] C. Lee, M. Potkonjak, W.H. Mangione-smith., Media Bench: a tool for evaluating and synthesizing multimedia and communications systems, in: International Symposium on Micro architecture, 1997.

- [24] M.R. Guthaus, J.S. Ringen berg, D. Ernst, T.M. Austin, T. Mudge, R.B. Brown, MiBench: a free, commercially representative embedded benchmark suite, International Workshop on Workload Characterization (WWC), 2001.

- [25] D. Burger, T. Austin, S. Bennet, Evaluating future microprocessors: the Simple scalar toolset, University of Wisconsin-Madison, Computer Science Department Technical Report CS-TR-1308, July 2000.

- [26] M. Rawlins, A. Gordon-Ross, On the interplay of loop caching, code compression, and cache configuration, ASP-DAC (2011).

- [27] CACTI, HP Labs, CACTI 4.2, http://www.hpl.hp.com/.