# A HYBRID MULTILEVEL INVERTER TOPOLOGY FOR PV SYSTEM WITH HIGH STEP UP DC-DC CONVERTER

# V S Prasadarao K<sup>1</sup> V JoshiManohar<sup>2</sup>

<sup>1</sup>Assistant Professor, K L University, Guntur, A.P, India-522502. <sup>2</sup>Professor, Guntur Engineering College, Guntur, A.P, India-. <sup>1</sup>Kvsprasad86@kluniversity.in <sup>2</sup>vjoshimanohar@gmail.com

### K V Krishna Rao

Assistant Professor, JIGJIGA University, Ethiopia. lakshmikrishna.99@gmail.com

Abstract: This paper presents a hybrid multilevel inverter for PV systems with high step up dc-dc converter with fewer power electronic components. The output voltage obtained from the PV system is low. To get the required high output voltage a high step up dc-dc converter is used in this paper. The step-up dc-dc converter uses only two switches to enhance the low voltage dc into high voltage. Grid interconnection of PV system requires an efficient inverter with reduced number of power electronic components. The presented hybrid MLI uses twelve switches for generating twentyone level ac output voltage. For getting the good response, the step-up dc-dc converter is implemented in closed loop configuration. To reduce the total harmonic distortion the presented hybrid MLI is controlled by sinusoidal PWM technique. Finally, the presented concept is verified with the matlab and simulink software and the appropriate results are presented.

*Key words:* dc-dc converter, multilevel inverter, PV system, PWM technique, Renewable energy sources.

## 1. Introduction

One of the most useful renewable energy source is because of its cleanness, light environmentally friendly [1]- [2]. But the output voltage obtained from the PV system is low. To get the high voltage a step -up dc-dc converter is needed. This paper presents a high step up dc- dc converter employing only two switches to step up the low voltage obtained the PV system. Grid interconnected PV system requires an appropriate inverter to satisfy grid requirements. The multilevel inverters are gaining more importance in now a days due to their ability to generate stair case waveform nearer to sine wave with imposing less stress on the switches. They are mainly used in the applications like grid connected renewable energy [3-5] systems, drive systems, and electric vehicles, etc. The conventional MLI topologies such as Diode clamped MLIs [6-10], Flying capacitor MLIs [11-13] and Cascaded H-bridge [14-15] MLIs can do this job with more number of power electronics components which increases the cost, switching losses there by reduces the inverter efficiency. The problem with the diode clamped MLI is it requires more number of diodes as the level increases and with that of flying capacitor MLI is capacitor voltage balancing. Cascaded H-bridge MLIs are very attractive because of its modularity and simple control. To overcome the above problems this paper presents a hybrid multilevel inverter with reduced number of components which generates twenty-one level output voltage at the output which are less compared to conventional MLI topologies. The proposed hybrid MLI is controlled by sinusoidal PWM technique which reduces the THD content. Finally, the PV system, step up dc-dc converter and hybrid MLIs are interfaced with each other.

# 2. High Step up DC-DC Converter

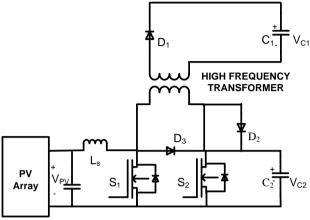

The following figure 1 shows the circuit diagram of high step up dc-dc converter. This high step up dc-dc converter enhance the low voltage of PV array into two different independent voltages. The output obtained from this dc-dc converter is used to feed the twenty-one level MLI. As seen in figure 1, this dc-dc converter comprises of boost converter and a current fed forward converter. The boost converter comprises of an inductor Ls and a diode D3, which charges the capacitor C2. The current fed converter consists of an inductor Ls, switches S1, S2, a high frequency transformer and the diodes D1 and D2. The dc-dc converter operates in two modes which are explained below.

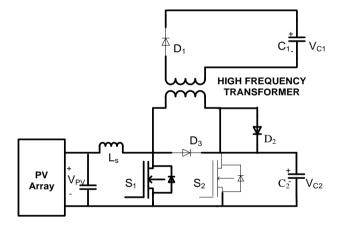

**Mode 1:** In this mode, switch S1 is turned on and S2 is turned off, D1, D3 are reverse biased, whereas the diode D2 is forward biased, which is shown in below figure 2. The PV gives the energy to the inductor Ls.

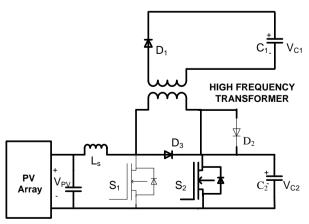

**Mode 2:** In this mode, switch S2 is turned on and S1 is turned off, D1, D3 are forward biased, whereas the

diode D2 is reverse biased, which is shown in below figure 3. Accordingly, C1 is connected in parallel with C2 through transformer, so energy stored in Ls and the PV array charges the capacitor C2 through D3 and charges the capacitor C1 through transformer and diode D1.

Fig.1: Circuit diagram of High Step up dc-dc converter

Fig. 2: Equivalent circuit diagram for mode 1

Fig. 3: Equivalent circuit diagram for mode 2

The voltage across the capacitor C2 is expressed as,

$$V_{c2} = \frac{1}{(1-D)} \frac{1}{V_{c}}$$

(1)

Similarly, the voltage across the capacitor C1 is expressed as,

$$V_{c1} = \frac{1}{2 \cdot (1 - D) V_{5}} \tag{2}$$

In this dc-dc converter, the energy stored in the inductor Ls is transferred to output capacitor C2 but not fed back to the dc source, the efficiency is improved.

# 3. Hybrid Multilevel Inverter

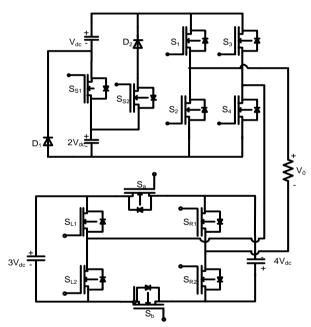

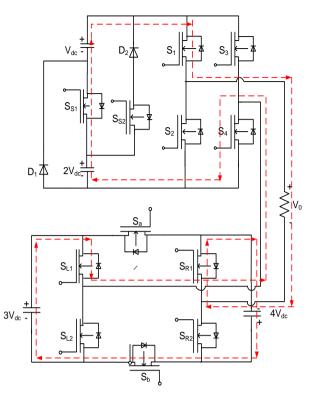

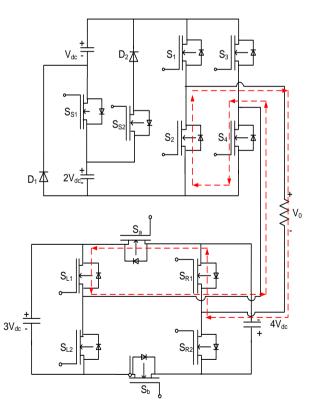

The following figure depicts the hybrid multilevel inverter, composed of two different inverters which are connected in series. This hybrid multilevel generates 21 levels across the output.

Fig. 4: Hybrid multilevel inverter

The following table illustrates the switching states for the presented hybrid multilevel inverter. four isolated dc sources to generate twenty- one level. The input for this inverter is taken from the PV system. The output voltage contains +Vdc, + 2Vdc, +3Vdc, +4Vdc, +5Vdc, +6Vdc, +7Vdc, +8Vdc, +9Vdc, +10Vdc levels in the positive half cycle and -Vdc, -2Vdc, -3Vdc, -4Vdc, -5Vdc, -6Vdc, -7Vdc, -8Vdc, -9Vdc, -10Vdc in the negative half cycle. By turn on the appropriate switches per table I, level of output voltage is obtained.

For example, to get +Vdc level, switches  $S_1$ ,  $S_4$ ,  $S_{R2}$ , and  $S_b$  are turn on. The presented hybrid MLI uses less number of switches compared to conventional MLI topologies which is shown in table II.

Table I: switching table for the hybrid multilevel inverter

| S <sub>S1</sub> | S <sub>S2</sub> | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | SLI | S <sub>L2</sub> | S <sub>R1</sub> | S <sub>R2</sub> | Sa | Sb | V <sub>0</sub>     |

|-----------------|-----------------|----------------|----------------|----------------|----------------|-----|-----------------|-----------------|-----------------|----|----|--------------------|

| 0               | 0               | 1              | 0              | 0              | 1              | 0   | 1               | 0               | 1               | 0  | 1  | $V_{DC}$           |

| 0               | 1               | 1              | 0              | 0              | 1              | 0   | 1               | 0               | 1               | 0  | 1  | 2V <sub>DC</sub>   |

| 1               | 0               | 1              | 0              | 0              | 1              | 0   | 1               | 0               | 1               | 0  | 1  | 3V <sub>DC</sub>   |

| 0               | 0               | 1              | 0              | 0              | 1              | 1   | 0               | 0               | 1               | 0  | 1  | 4V <sub>DC</sub>   |

| 0               | 1               | 1              | 0              | 0              | 1              | 1   | 0               | 0               | 1               | 0  | 1  | 5V <sub>DC</sub>   |

| 1               | 0               | 1              | 0              | 0              | 1              | 1   | 0               | 0               | 1               | 0  | 1  | 6V <sub>DC</sub>   |

| 0               | 0               | 0              | 1              | 0              | 1              | 1   | 0               | 1               | 0               | 0  | 1  | 7V <sub>DC</sub>   |

| 0               | 0               | 1              | 0              | 0              | 1              | 1   | 0               | 1               | 0               | 0  | 1  | 8V <sub>DC</sub>   |

| 0               | 1               | 1              | 0              | 0              | 1              | 1   | 0               | 1               | 0               | 0  | 1  | 9V <sub>DC</sub>   |

| 1               | 0               | 1              | 0              | 0              | 1              | 1   | 0               | 1               | 0               | 0  | 1  | 10V <sub>DC</sub>  |

| 0               | 0               | 0              | 1              | 0              | 1              | 1   | 0               | 1               | 0               | 1  | 0  | 0                  |

| 0               | 1               | 0              | 1              | 1              | 0              | 1   | 0               | 1               | 0               | 1  | 0  | -V <sub>DC</sub>   |

| 0               | 0               | 0              | 1              | 1              | 0              | 1   | 0               | 1               | 0               | 1  | 0  | -2V <sub>DC</sub>  |

| 1               | 0               | 0              | 1              | 1              | 0              | 1   | 0               | 1               | 0               | 1  | 0  | -3V <sub>DC</sub>  |

| 0               | 0               | 0              | 1              | 1              | 0              | 0   | 1               | 1               | 0               | 1  | 0  | -4V <sub>DC</sub>  |

| 0               | 1               | 0              | 1              | 1              | 0              | 0   | 1               | 1               | 0               | 1  | 0  | -5V <sub>DC</sub>  |

| 1               | 0               | 0              | 1              | 1              | 0              | 0   | 1               | 1               | 0               | 1  | 0  | -6V <sub>DC</sub>  |

| 0               | 0               | 0              | 1              | 0              | 1              | 0   | 1               | 0               | 1               | 1  | 0  | -7V <sub>DC</sub>  |

| 0               | 0               | 0              | 1              | 1              | 0              | 0   | 1               | 0               | 1               | 1  | 0  | -8V <sub>DC</sub>  |

| 0               | 1               | 0              | 1              | 1              | 0              | 0   | 1               | 0               | 1               | 1  | 0  | -9V <sub>DC</sub>  |

| 1               | 0               | 0              | 1              | 1              | 0              | 0   | 1               | 0               | 1               | 1  | 0  | -10V <sub>DC</sub> |

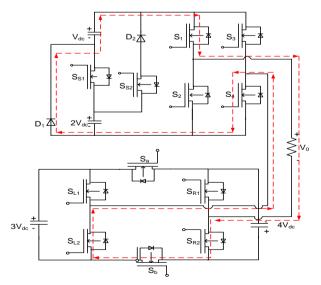

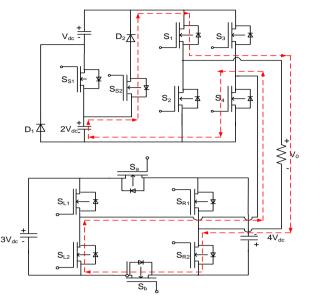

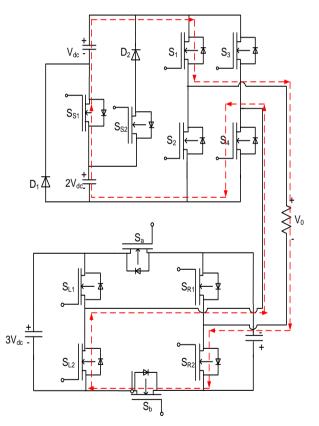

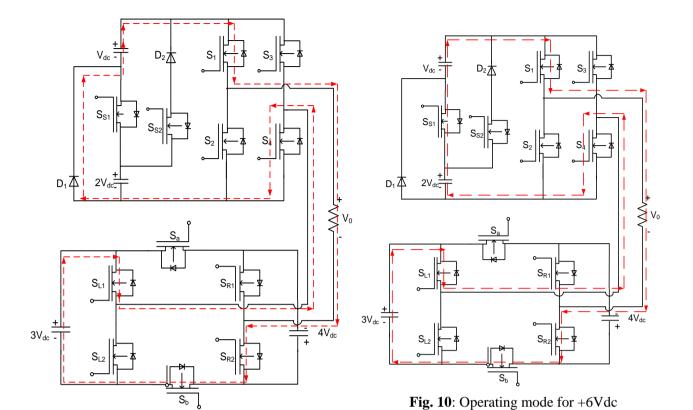

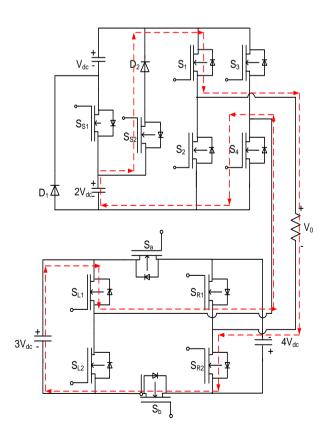

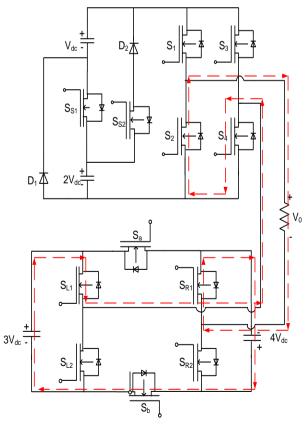

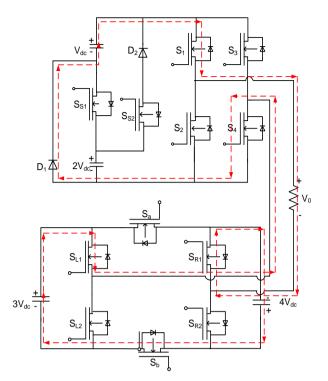

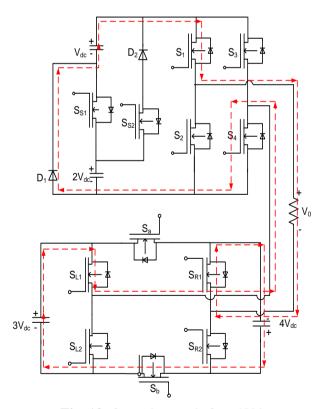

The following figures illustrates the switching combinations for each level in positive half cycle and the same can be represented for the negative cycle also.

Fig. 5: Operating mode for +Vdc

Fig. 6: Operating mode for +2Vdc

Fig. 7: Operating mode for +3Vdc

Fig. 8: Operating mode for +4Vdc

Fig. 9: Operating mode for +5Vdc

Fig. 11: Operating mode for +7Vdc

Fig. 12: Operating mode for +8Vdc

Fig. 13: Operating mode for +9Vdc

Fig. 14: Operating mode for +10Vdc

Fig. 15: Operating mode for Zero level

The following table shows the comparison between proposed MLI topology and Conventional MLI topologies interms of requirement of power switches, diodes and capacitors.

Table II: Comparison Between Proposed MLI and Traditional MLI topologies

| Traditional WEST topologies |          |          |            |  |  |  |  |  |  |

|-----------------------------|----------|----------|------------|--|--|--|--|--|--|

| Type of                     | Power    | Clamping | Balancing  |  |  |  |  |  |  |

| MLI                         | Switches | Diodes   | Capacitors |  |  |  |  |  |  |

| Diode                       |          |          |            |  |  |  |  |  |  |

| Clamped                     | 16       | 14       | 0          |  |  |  |  |  |  |

| MLI                         |          |          |            |  |  |  |  |  |  |

| Flying                      |          |          |            |  |  |  |  |  |  |

| Capacitor                   | 16       | 0        | 7          |  |  |  |  |  |  |

| MLI                         |          |          |            |  |  |  |  |  |  |

| Cascaded                    |          |          |            |  |  |  |  |  |  |

| H- Bridge                   | 16       | 0        | 0          |  |  |  |  |  |  |

| MLI                         |          |          |            |  |  |  |  |  |  |

| Proposed                    | 12       | 2        | 0          |  |  |  |  |  |  |

| MLI                         | 12       | 4        |            |  |  |  |  |  |  |

From table II, the proposed MLI topology requires less number of power switches, clamping diodes, and capacitors compared to conventional MLIs, which reduces the driver circuits and installation space.

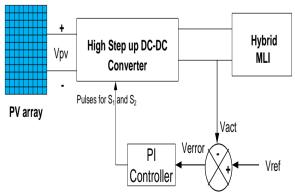

## 4.Proposed System

The following figure shows the proposed overall system. It consists of PV array which is the input for the high step up dc-dc converter and hybrid multilevel inverter whose input is taken from the dc-dc converter. To get the good response, the step-up dc-dc converter is operated in closed loop manner.

**Fig. 16**: Hybrid MLI with step up dc-dc converter for PV system

## 5. Simulation Results

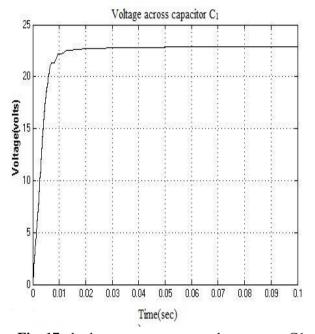

The presented system is verified by using Matlab/Simulink software. The following figure shows the output voltage waveforms of high step up dc-dc converter.

Fig. 17: dc-dc converter output voltage across C1

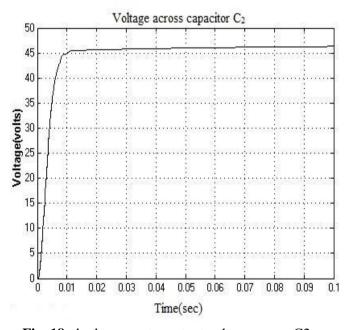

Fig. 18: dc-dc converter output voltage across C2

In this paper the voltage obtained from the PV system is converted into two independent different voltages using step up dc-dc converter. By proper tuning of the PI controller, required output voltage of step up dc-dc converter is obtained.

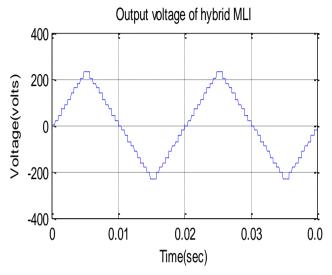

The following figure depicts the output voltage of 21 level hybrid MLI without PWM technique. The parameters considered here are as follows:  $V_1 = 23V$ ,  $V_2 = 46V$ ,  $V_3 = 69$ ,  $V_4 = 92$ , switching frequency = 3050 Hz and load  $R = 100\Omega$ .

**Fig. 19**: output voltage of 21 level hybrid MLI without PWM technique

**Fig. 20**: Harmonic spectrum of 21 level hybrid MLI without PWM technique

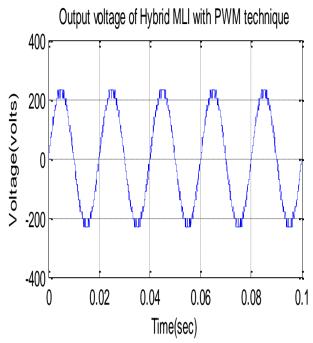

From the figure 20, the THD content of the presented hybrid MLI without employing PWM technique is 12.98% which is not under the limits of IEEE-519 rule. To reduce the THD content PWM technique is employed. The following figure the shows the output voltage of Hybrid MLI with level shifted Carrier PWM

technique with modulation index is maintained at 1.

**Fig. 21**: Output voltage of 21 level hybrid MLI with carrier based PWM technique

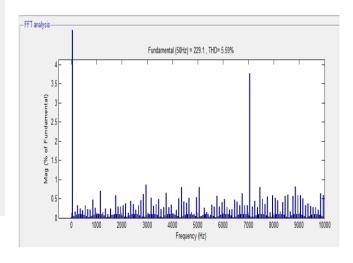

The following shows the harmonic spectrum of Hybrid MLI with carrier PWM technique. From the figure 22, THD content is reduced to 5.59%.

**Fig. 22**: Harmonic spectrum of 21 level hybrid MLI with carrier based PWM technique

By changing the value of modulation index (ma), the THD content can be varied which is shown in below table.

Table II: Modulation Index versus THD content

| <b>Modulation Index(ma)</b> | %THD  |

|-----------------------------|-------|

| 1                           | 5.59  |

| 0.9                         | 6.27  |

| 0.8                         | 6.77  |

| 0.7                         | 7.71  |

| 0.6                         | 9.16  |

| 0.5                         | 10.81 |

#### 6.Conclusion

A hybrid multilevel inverter topology with high step up dc-dc converter employing less number of components for PV system is presented in this paper. Due to less number of components employed in the system, the switching losses and cost is also low. The presented step up dc-dc converter uses only two switches for power conversion and also it acts as a single input multiple output (SIMO) converter which can drive the different loads. Better response from the high step up dc-dc converter can be obtained by proper selection of gains K<sub>P</sub> and K<sub>i</sub> values. The presented hybrid MLI produces 21 levels in the output voltage with 12 switches only which are very less when compared to the existing multilevel inverter topologies. Low value of THD content of presented hybrid MLI is also obtained with the implementation of carrier based PWM technique

## References

- [1] T. Shimizu, O. Hashimoto And G. Kimura, "A Novel High Performance Utility Interactive Photovoltaic Inverter System," IEEE Transactions on Power Electronics. America, Vol. 18, Pp. 704–711, March 2003.

- [2] Y. K. Chen, C. H. Yang and Y. C. Wu, "Robust Fuzzy Controlled Photovoltaic Power Inverter with Taguchi Method," IEEE Transaction on Aerospace and Electronic Systems. America, Vol. 38, Pp. 940–954, July 2002.

- [3] K. Bandara, T. Sweet, And J. Ekanayake, "Photovoltaic Applications for Off-Grid Electrification Using Novel Multi-Level Inverter Technology with Energy Storage," Renew. Energy, Vol. 37, No. 1, Pp. 82–88, Jan. 2012.

- [4] J. Chavarria, D. Biel, F. Guinjoan, C. Meza, And J. J. Negroni, "Energy Balance Control of PV Cascaded Multilevel Grid-Connected Inverters Under Level-Shifted and Phase-Shifted PWM," IEEE Trans. Ind. Electron., Vol. 60, No. 1, Pp. 98–111, Jan. 2013.

- [5] N. A. Rahim, K. Chaniago, And J. Selvaraj, "Single-Phase Seven-Level Grid-Connected Inverter for Photovoltaic System," IEEE Trans. Ind. Electron., Vol.

- 58, No. 6, Pp. 2435-2443, Jun. 2011.

- [6] K. Hasegawa And H. Akagi, "Low-Modulation-Index Operation of a Five Level Diode-Clamped PWM inverter With a Dc-Voltage-Balancing Circuit for A Motor Drive," IEEE Trans. Power Electron., Vol. 27, No. 8, Pp. 3495–3505, Aug. 2012.

- [7] E. Pouresmaeil, D. Montesinos-Miracle, And O. Gomis-Bellmunt, "Control Scheme of Three-Level NPC Inverter for Integration of Renewable Energy Resources into AC Grid," IEEE Syst. J., Vol. 6, No. 2, Pp. 242–253, Jun. 2012.

- [8] S. Srikanthan And M. K. Mishra, "DC Capacitor Voltage Equalization in Neutral Clamped Inverters for DSTATCOM Application," IEEE Trans. Ind. Electron., Vol. 57, No. 8, Pp. 2768–2775, Aug. 2010.

- [9] M. Chaves, E. Margato, J. F. Silva, And S. F. Pinto, "New Approach in Back-To-Back M-Level Diode clamped Multilevel Converter Modelling and Direct Current Bus Voltages Balancing," IET Power Electron., Vol. 3, No. 4, Pp. 578–589, 2010.

- [10] Dr. Obbu Chandra Sekhar Dr.K Chandra Sekhar Dr.G Durga Sukumar, "An Enhanced DTC Scheme For Induction Machine Control Fed By Seven-Level MPC Voltage Source Inverter", Journal Of Electrical Engineering (Jee)-2014, Vol 14. No 2, Pp.180-185.

- [11] A. K. Sadigh, S. H. Hosseini, M. Sabahi, And G. B. Gharehpetian, "Double Flying Capacitor Multicell Converter Based on Modified Phase-Shifted Pulse Width Modulation," IEEE Trans. Power Electron., Vol. 25, No. 6, Pp. 1517–1526, Jun. 2010.

- [12] S. Thielemans, A. Ruderman, B. Reznikov, And J. Melkebeek, "Improved Natural Balancing with Modified Phase-Shifted PWM For Single-Leg Five level Flying-Capacitor Converters," IEEE Trans. Power Electron., Vol. 27, No. 4, Pp. 1658–1667, Apr. 2012.

- [13] S. Choi And M. Saeedifard, "Capacitor Voltage Balancing of Flying Capacitor Multilevel Converters by Space Vector PWM," IEEE Trans. Power Delivery, Vol. 27, No. 3, Pp. 1154–1161, Jul. 2012.

- [14] L. Maharjan, T. Yamagishi, And H. Akagi, "Active-Power Control of Individual Converter Cells for A Battery Energy Storage System Based on A Multilevel Cascade PWM Converter," IEEE Trans. Power Electron., Vol. 27, No. 3, Pp. 1099–1107, Mar. 2012.

- [15] X. She, A. Q. Huang, T. Zhao, And G. Wang, "Coupling Effect Reduction of a Voltage-Balancing Controller" IEEE Trans. Power Electron., Vol. 27, No. 8, Pp. 3530–3543, Aug. 2012.