# A NEW MULTILEVEL INVERTER WITH MINIMUM NUMBER OF SWITCHES AND REDUCTION IN THD

V. Thiyagarajan<sup>1</sup>, P. Somasundaram<sup>2</sup>

<sup>1</sup>Assistant Professor, Department of EEE, SSN College of Engineering, Kalavakkam, Tamilnadu, India.

<sup>2</sup>Associate Professor, Department of EEE, CEG, Anna University, Chennai, Tamilnadu, India.

Email: thiyagarajanv@ssn.edu.in

**Abstract:** The main objective of this paper is to propose a new single phase asymmetrical type multilevel inverter with minimum number of switches. The proposed multilevel inverter consists of level creator unit which generate only positive levels of outputs. The H-bridge inverter is added to change the polarity of the output voltage. The comparison between the proposed topology with existing inverter topologies is presented. The proposed inverter consist of six voltage sources, 11 main switches and 4 H-bridge inverter switches. Different algorithms are used to calculate the switching angles and the results are compared with the reference. The proposed inverter produces output voltage waveform with minimum THD as compared with the reference. The computer based simulation model is developed using MATLAB/SIMULINK software to verify the function of the proposed inverter.

**Key words:** Multilevel inverter, Switching angle, Symmetric, Asymmetric, THD.

# 1. Introduction

The concept of multilevel inverters is introduced in 1975 [1]. The term 'multilevel' began with threelevel converter and then several multilevel topologies have been proposed over the last few decades. The basic concept of multilevel inverter is to synthesize the staircase output voltage from the several low or medium DC voltage sources. It achieves high power ratings and enables the use of renewable energy resources, capacitors or batteries as inputs. It has received major interest by the researchers because of their inherent advantageous features such as low distortion, high power quality, low dv/dt stress, minimum switching losses and better electromagnetic interference [2]. The major drawback of the multilevel inverter is it requires greater number of power electronic switches and associated gate driver circuit to achieve higher output levels.

The conventional topologies of multilevel inverters are diode-clamped, flying capacitor and cascaded H-bridge inverters[2-6]. In diode-clamped multilevel inverters, diodes are used as a clamping devices. The n-level diode-clamped multilevel inverters requires n-1 switching pairs and n-1 capacitors for clamping DC voltage[2]. The switches are operate at low switching frequency. The main advantage is that the diode transfers very limited

amount of voltage and thereby reduces the stress on the switching devices. However, it requires more number of clamping diodes to achieve higher level of output voltage and hence increases the cost and size. The capacitor clamped multilevel inverter uses capacitors instead of clamping diodes which controls both the real and reactive power flow. The large number of clamping capacitors helps to ride through short duration outages and deep voltage sags [3]. The major drawbacks includes need of large number of storage capacitors, pre-charging of capacitors, high switching losses, poor efficiency, more expensive and bulky. The cascade H-bridge multilevel inverter consists of full H-bridges with independent DC voltage sources. Each full Hbridges provide three different levels of voltages like zero, positive DC and negative DC voltages. The main advantages include robustness and ease of The number of output voltage levels depends on the number of individual H-bridges and is given by 2k+1, where k is the number of Hbridges[4-6]. The multilevel inverter can be symmetric or asymmetric. In symmetric multilevel inverter, the values of all DC voltage sources are equal and has the advantage of high modularity. However, the values of DC voltage sources are different in asymmetrical inverter and hence it loses modularity.

Modern-day researchers focused on developing new topologies of multilevel inverters, novel pulsewidth modulation (PWM) techniques and improved control techniques for various applications. This paper proposes a new multilevel inverter with reduction in number of power electronic switches. The proposed inverter produces 33 level output voltage during asymmetrical mode with minimum THD. The simulation results are presented in Section-5.

# 2. Existing Multilevel Inverter Topologies

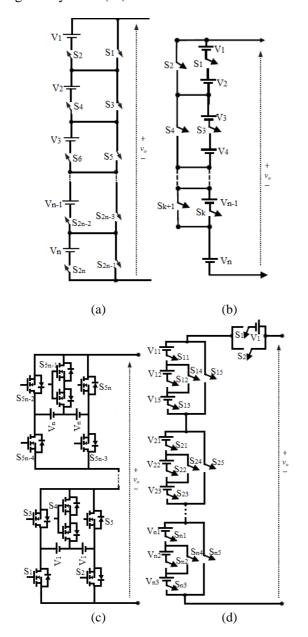

The asymmetric multilevel inverter proposed in [7] is shown in Fig.1(a). This inverter able to bypass or conduct the DC voltage sources separately to generate the desired voltage levels. The relation between the number of levels 'n' and number of switches 'ns' used is given by  $n = 2^{(ns-2)/2} - 1$ . Fig. 1(b) shows double source sub-multilevel inverter

proposed in [8]. This topology consists of level generator unit and polarity changing unit. The level generating unit consists of single and double source sub multilevel inverter and H-bridge inverter acts as a polarity changer. The drawback of this topology is it have separate structure for even and odd number of DC voltage sources. The relation between the number of levels 'n' and number of switches 'ns' used is given by n = 2(ns)-7.

Fig. 1. Existing topologies of Multilevel Inverter (a) Ref.[7], (b) Ref. [8], (c) Ref. [9] and (d) Ref. [10].

The cascaded sub-multilevel cells based inverter proposed in Ref.[9] is shown in Fig. 1(c). It operates in both symmetric and asymmetric state. This topology needs minimum number of bi-directional switches and great number of IGBTs. This paper

presented four different algorithms to calculate the magnitude of DC voltage sources. Another topology of multilevel inverter proposed in Ref. [10] is shown in Fig. 1 (d). The basic unit consists of three DC voltage sources and five switches to achieve five level output voltage. The major drawback of this topology is it is not able to generate  $V_{\rm dc}$  level of voltage. To achieve this level, an additional DC voltage source of amplitude Vdc and two unidirectional power switches are connected in series with the basic units.

In this paper, the new topology of multilevel inverter with reduced number of power switches have been proposed. The proposed inverter achieves 33 level output voltage during asymmetrical mode with 15 switches and 6 DC voltage sources.

# 3. Proposed Multilevel Inverter

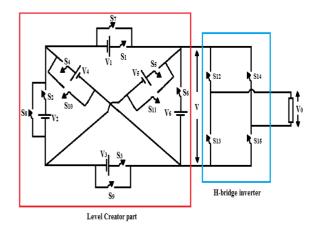

The proposed asymmetric type 33-level inverter topology is shown in Fig. 2.

Fig. 2. Proposed topology of Multilevel Inverter

The proposed inverter consists of two units: (1) level creator unit and (2) polarity changing unit. The level creator unit consist of 6 DC voltage sources and 11 switches. This level creator unit produces unidirectional output voltage with various voltage levels as 0,  $V_{dc}$ ,  $2V_{dc}$ ,... and  $16V_{dc}$ . The voltage magnitude of each DC voltage sources are different. The polarity changing unit is simply a H-bridge inverter which helps to convert the unidirectional output voltage of the level creator unit into bidirectional output voltage. When the switches  $S_{12}$ and S<sub>15</sub> are ON, positive levels of voltages are obtained and when  $S_{13}$  and  $S_{14}$  are ON, negative levels of voltages are obtained. Hence, the proposed multilevel inverter with level creator unit and polarity changing unit can able to produce 33 level of output voltage such as -16  $V_{\text{dc}},$  -15  $V_{\text{dc}},$  . . . , -  $V_{\text{dc}},$ 0,  $V_{dc,\cdot}$  . .,  $15V_{dc}$  and  $16V_{dc}$ . The magnitude of DC voltage sources are :  $V_1$ =  $V_{dc}$ ,  $V_2$ =  $4V_{dc}$ ,  $V_3$ =

$10V_{dc}, V_4 = 7V_{dc}, V_5 = 6V_{dc}, \text{ and } V_6 = 12V_{dc}.$  The switching states for the level creator unit of the proposed multilevel inverter during asymmetrical mode are given in Table 1. When the switches  $S_{12}$ and  $S_{15}$  are ON, 16 levels of positive voltages are obtained with the above mentioned switching states. Similarly, when  $S_{13}$  and  $S_{14}$  are ON, 16 levels of negative voltages are obtained with the above mentioned switching states. The zero level is also obtained for any of the following switching conditions: (1)  $S_{12}$  and  $S_{14}$  are OFF and (2)  $S_{13}$  and S<sub>15</sub> are OFF. At any switching condition, maximum 3 switches of the level creator unit are ON. Therefore, the total number of conduction switches for the proposed inverter topology is 5 i.e., three switches in the level creator part and 2 switches in the polarity changing unit.

Table 1 Switching states

| Witching<br>Voltage | $S_1$ | $S_2$ | $S_3$ | S <sub>4</sub> | $S_5$ | S <sub>6</sub> | S <sub>7</sub> | $S_8$ | S <sub>9</sub> | S <sub>10</sub> | S <sub>11</sub> |

|---------------------|-------|-------|-------|----------------|-------|----------------|----------------|-------|----------------|-----------------|-----------------|

| 16V <sub>dc</sub>   | 0     | 0     | 1     | 0              | 1     | 0              | 0              | 0     | 0              | 0               | 0               |

| 15V <sub>dc</sub>   | 1     | 1     | 1     | 0              | 0     | 0              | 0              | 0     | 0              | 0               | 0               |

| $14V_{dc}$          | 0     | 1     | 1     | 0              | 0     | 0              | 1              | 0     | 0              | 0               | 0               |

| $13V_{dc}$          | 0     | 0     | 0     | 1              | 1     | 0              | 0              | 1     | 0              | 0               | 0               |

| $12V_{dc}$          | 0     | 0     | 0     | 0              | 1     | 0              | 0              | 0     | 0              | 0               | 0               |

| $11V_{dc}$          | 1     | 0     | 1     | 0              | 0     | 0              | 0              | 1     | 0              | 0               | 0               |

| $10V_{dc}$          | 0     | 0     | 1     | 0              | 0     | 0              | 1              | 1     | 0              | 0               | 0               |

| $9V_{dc}$           | 0     | 1     | 0     | 1              | 1     | 0              | 0              | 0     | 0              | 0               | 0               |

| $8V_{dc}$           | 1     | 0     | 0     | 1              | 0     | 0              | 0              | 0     | 0              | 0               | 0               |

| $7V_{dc}$           | 0     | 0     | 0     | 1              | 0     | 0              | 1              | 0     | 0              | 0               | 0               |

| $6V_{dc}$           | 0     | 0     | 0     | 0              | 1     | 0              | 0              | 0     | 1              | 0               | 0               |

| $5V_{dc}$           | 1     | 1     | 0     | 0              | 0     | 0              | 0              | 0     | 1              | 0               | 0               |

| $4V_{\text{dc}}$    | 0     | 1     | 0     | 0              | 0     | 0              | 1              | 0     | 1              | 0               | 0               |

| $3V_{dc}$           | 0     | 1     | 0     | 1              | 0     | 0              | 0              | 0     | 0              | 0               | 1               |

| $2V_{dc}$           | 0     | 1     | 0     | 0              | 1     | 0              | 0              | 0     | 0              | 1               | 0               |

| $V_{dc}$            | 1     | 0     | 0     | 0              | 0     | 0              | 0              | 0     | 0              | 1               | 0               |

| 0                   | 0     | 0     | 0     | 0              | 0     | 0              | 1              | 1     | 1              | 0               | 0               |

The comparison of the output voltage levels with the number of DC voltage sources and the number of switches for different multilevel inverter topologies are given in Table 2. The comparison of power components requirements for 33-level inverter is given in Table 3.

Table 2

Comparison of different Multilevel Inverters

| Inverter          | Number<br>of DC<br>Sources | Number<br>of<br>Switches | Number<br>of level | ON state<br>switches |

|-------------------|----------------------------|--------------------------|--------------------|----------------------|

| [14]              | 6                          | 12                       | 23                 | 5                    |

| [15]              | 6                          | 12                       | 25                 | 5                    |

| [16]              | 6                          | 14                       | 17                 | 6                    |

| [17]              | 6                          | 16                       | 23                 | 8                    |

| [18]              | 6                          | 16                       | 31                 | 8                    |

| [19]              | 6                          | 18                       | 29                 | 9                    |

| Proposed inverter | 6                          | 15                       | 33                 | 5                    |

Table 3 Comparison of power components requirements for 33-level inverter

| Inverter | Number<br>of DC<br>sources | Maximum<br>output<br>voltage | of<br>switches<br>(IGBTs<br>and | Maximum Voltage rating of main switches | Voltage<br>rating of<br>Half-<br>bridge<br>switches |

|----------|----------------------------|------------------------------|---------------------------------|-----------------------------------------|-----------------------------------------------------|

| [14]     | 8                          | 16V <sub>dc</sub>            | drivers)                        | 14V <sub>dc</sub>                       | 16V <sub>dc</sub>                                   |

| Proposed | 6                          | 16V <sub>dc</sub>            | 15                              | $14V_{dc}$                              | 16V <sub>dc</sub>                                   |

It is observed that, the presented inverter topology requires same number of switches to synthesize the 33- level output voltage as compared with [14]. In addition, the rating of these switches are also same. However, the topology presented in [14] requires greater number of voltage sources to synthesize 33-level output voltage as compared with the proposed inverter topology. From the above table, it is clear that the proposed multilevel inverter uses minimum number of switches and DC voltage sources to achieve higher output voltage level. In addition, it is also observed that the number of switches in the current conduction path for the proposed inverter topology is very less as compared with other presented topologies. This helps to reduce the switching losses and thereby increases the efficiency of the inverter.

## 4. Switching Angle Calculation

Switching angles plays an important role in the reduction of total harmonic distortion (THD). For 'n' level inverter, 2(n-1) switching angles has to be determined [11]. The switching angles corresponding to the period 0° to 90° are called as main switching angles. An 'n' level inverter has (n-1)/2 main switching angles. It is enough to determine the (n-1)/2 main switching angles and the other switching angles are obtained from the main switching angles using the following relations [11, 12]:

1. For period

$$0^{\circ}$$

to  $90^{\circ}$

$$=\theta_1,\,\theta_2,\,\,\ldots,\,\theta_{(n\text{-}1)/2}.$$

2. For period 90° to 180°

$$=\theta_{(n+1)/2},\dots,\ \theta_{(n-1)},=(\pi-\theta_{(n-1)/2}),\dots,(\pi-\theta_1).$$

3. For period  $180^o$  to  $270^o$

$$=\theta_n,\ldots,\theta_{3(n\text{-}1)/2}=(\pi+\theta_1),\ldots,(\pi+\theta_{(n\text{-}1)/2}).$$

4. For period 270° to 360°

$$=\theta_{(3n-1)/2},\ldots,\theta_{2(n-1)}=(2\pi-\theta_{(n-1)/2}),\ldots,(2\pi-\theta_1).$$

Algorithm - 1

$$\theta_{k} = k \frac{180^{\circ}}{n}, k = 1, 2, ..., \left(\frac{n-1}{2}\right)$$

Algorithm - 2

$$\theta_{k} = k \frac{180^{\circ}}{n+1}, k = 1, 2, ..., \left(\frac{n-1}{2}\right)$$

Algorithm - 3  $\theta_k = \frac{1}{2} \sin^{-1} \left( \frac{2k-1}{n-1} \right), k = 1, 2, ..., \left( \frac{n-1}{2} \right)$ Algorithm - 4

$$\theta_k = \sin^{-1}\left(\frac{2k-1}{n-1}\right), k = 1, 2, ..., \left(\frac{n-1}{2}\right)$$

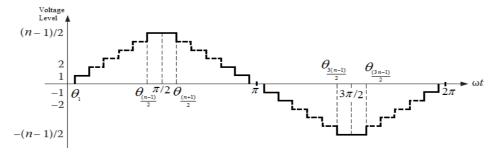

The switching angles of n-level inverter is shown in Fig. 3. For the proposed multilevel inverter, there are 16 main switching angles and are determined using the different algorithms given below [11]. The 16 main switching angles for the proposed multilevel inverter obtained using the above mentioned algorithms are given in Table 4.

Fig. 3. Output Voltage with switching angles of 'n' level inverter

Table 4 Switching Angles

|               | Switching Angles (in degree) |           |           |           |  |  |

|---------------|------------------------------|-----------|-----------|-----------|--|--|

| Angle         | Algorithm                    | Algorithm | Algorithm | Algorithm |  |  |

|               | - 1                          | - 2       | - 3       | - 4       |  |  |

| $\theta_1$    | 5.4545                       | 5.2941    | 0.8954    | 1.7908    |  |  |

| $\theta_2$    | 10.9091                      | 10.5882   | 2.6897    | 5.3794    |  |  |

| $\theta_3$    | 16.3636                      | 15.8824   | 4.4946    | 8.9893    |  |  |

| $\theta_4$    | 21.8182                      | 21.1765   | 6.3178    | 12.6356   |  |  |

| $\theta_5$    | 27.2727                      | 26.4706   | 8.1674    | 16.3348   |  |  |

| $\theta_6$    | 32.7273                      | 31.7647   | 10.0528   | 20.1055   |  |  |

| $\theta_7$    | 38.1818                      | 37.0588   | 11.9847   | 23.9695   |  |  |

| $\theta_8$    | 43.6364                      | 42.3529   | 13.9766   | 27.9532   |  |  |

| $\theta_9$    | 49.0909                      | 47.6471   | 16.045    | 32.09     |  |  |

| $\theta_{10}$ | 54.5455                      | 52.9412   | 18.2118   | 36.4236   |  |  |

| $\theta_{11}$ | 60                           | 58.2353   | 20.5072   | 41.0145   |  |  |

| $\theta_{12}$ | 65.4545                      | 63.5294   | 22.9757   | 45.9514   |  |  |

| $\theta_{13}$ | 70.9091                      | 68.8235   | 25.6876   | 51.3752   |  |  |

| $\theta_{14}$ | 76.3636                      | 74.1176   | 28.7691   | 57.5383   |  |  |

| $\theta_{15}$ | 81.8182                      | 79.4118   | 32.4961   | 64.9922   |  |  |

| $\theta_{16}$ | 87.2727                      | 84.7059   | 37.8192   | 75.6385   |  |  |

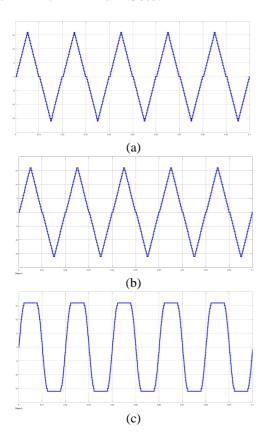

The switching pulses generated using the different algorithms are shown in Fig. 4.

Fig. 4. Gate pulses generated using (a) Algorithm - 1 (b) Algorithm- 2 (c) Algorithm-3 and (d) Algorithm- 4

#### 5. Simulation Results

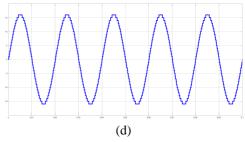

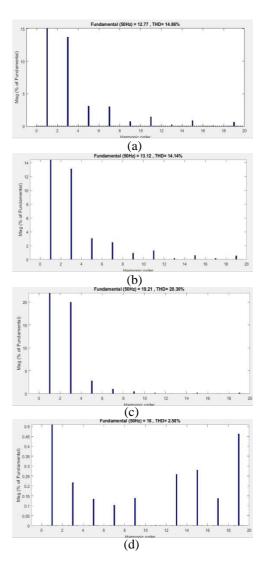

The simulation results are presented in this section. The different voltage sources have values  $V_1$ =1V,  $V_2$ =4V,  $V_3$ =10V,  $V_4$ =7V,  $V_5$ =6V, and  $V_6$ =12V. The maximum output voltage obtained is 16V (i.e.  $V_3$ + $V_5$ ). The output voltage of the proposed multilevel inverter for different algorithms are shown in Fig. 5. The result shows that the algorithm - 4 gives the output voltage similar to the sinusoidal output. The output voltage has 33 levels (i.e., 16 positive, 16 negative and 1 zero). The FFT analysis of the output voltage of the proposed multilevel inverter for different algorithms are shown in Fig. 6. The result shows that algorithm - 4 gives minimum THD of 2.50%.

Fig. 5. Output Voltage (a) Algorithm - 1 (b) Algorithm - 2 (c) Algorithm -3 and (d) Algorithm - 4.

Fig. 6.FFT Analysis (a) Algorithm - 1 (b) Algorithm - 2 (c) Algorithm - 3 and (d) Algorithm - 4

Table 5 shows the comparison of the THD of the output voltage waveform obtained using different algorithms with Ref. [11] .

Table 5 Comparison of THD

| IISUII OI TIID |          |          |  |  |  |

|----------------|----------|----------|--|--|--|

| Algorithm      | THD (%)  |          |  |  |  |

| Algorithm      | Ref.[11] | Proposed |  |  |  |

| Algorithm - 1  | 14.26    | 14.86    |  |  |  |

| Algorithm - 2  | 13.35    | 14.14    |  |  |  |

| Algorithm - 3  | 20.46    | 20.30    |  |  |  |

| Algorithm - 4  | 4.39     | 2.50     |  |  |  |

The above table shows that the proposed multilevel inverter achieves minimum THD for algorithm - 4. The proposed inverter also achieves higher output level with minimum number of switches and DC voltage sources. The measured input and output powers are about 500W and 466 W, respectively with the loss of 34W. Therefore, the efficiency of the proposed inverter is about 93.2%.

#### 6. Conclusion

A new topology of multilevel inverter is proposed in this paper. The proposed inverter achieves 33 level output voltage with 6 DC voltage sources, 11 main switches and 4 H-bridge switches. Each voltage sources have different voltage magnitudes. The switching angles are determined using four different algorithms. A comparison of the proposed inverter topology with other existing topologies is presented in this paper. The performance of the proposed inverter is analysed using MATLAB software and the result exhibit the good performance and feasibility of the proposed inverter. The result shows that maximum voltage obtained is 16Vdc and the algorithm - 4 achieves minimum THD of the output voltage waveform.

### References

- [1] Baker, R. H. and Bannister, L. H.: *Electric Power Converter*. In: U.S. Patent 3 867 643, Feb. 1975.

- [2] Boora, A. A., Nami, A., Zare, F., Ghosh, A. and Blaabjerg, F.: Voltage sharing converter to supply single-phase asymmetric four-level diode clamped inverter with high power factor loads. In: IEEE Trans. Power Electron., vol. 25, no. 10, pp. 2507–2520, Oct. 2010.

- [3] Khazraei, M., Sepahvand, H., Corzine, K. A. and Ferdowsi, M.: Active Capacitor Voltage Balancing in Single-Phase Flying-Capacitor Multilevel Power Converters. In:IEEE Transactions on Industrial Electronics, vol. 59, no. 2, pp. 769-778, Feb. 2012.

- [4] Rodriguez, J., Bernet, S., Steimer, P. and Lizama, I.: *A survey on natural point clamped inverters.* In: IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2219–2230, Jul. 2010.

- [5] Ding, K., Cheng, K. W. E., and Zou, Y. P.: Analysis of an asymmetric modulation methods for cascaded

- multilevel inverters. In. IET Power Electron., vol. 5, no. 1, pp. 74–85, Jan. 2012.

- [6] Babaei, E., Kangarlu, M. F., Sabahi, M. and Alizadeh Pahlavani, M. R.: *Cascaded multilevel inverter using sub-multilevel cells*. In. Electr. Power Syst. Res., vol. 96, pp. 101–110, Mar. 2013.

- [7] Babaei, E., Kangarlu, M. F. and Mazgar, F.N: Symmetric and asymmetric multilevel inverter topologies with reduced switching devices. In: Electric Power Systems Research, vol. 86, pp. 122–130, 2012.

- [8] Ramani, K., Sathik, M. A. J., and Sivakumar, S.: A New Symmetric Multilevel Inverter Topology Using Single and Double Source Sub-Multilevel Inverters. In: Journal of Power Electronics, vol. 15, No. 1, pp. 96-105, January 2015.

- [9] Banaei, M. R., and Salary, E.: Asymmetric Cascaded Multi-level Inverter: A Solution to Obtain High Number of Voltage Levels. In. Journal of Elect. Engg. Technol., vol. 8, No. 2, pp. 316-325, 2013.

- [10] Babaei, E., Laali, S. and Bayat, Z.: A Single-Phase Cascaded Multilevel Inverter Based on a New Basic Unit With Reduced Number of Power Switches. In: IEEE Trans. on Indus. Elect., vol. 62, no. 2, pp-922-929, 2015.

- [11] Luo F. L. and Ye H.: *Advanced DC/AC Inverters*. In: CRC Press LLC, 2013.. ISBN: 978-1-4665-1138-5.

- [12] Thiyagarajan, V. and Somasundaram, P.: New Asymmetric Seven Level Inverter with Minimum Number of Voltage Sources and Switches. In. Journal of Electrical Engineering, vol.17, no. 3, pp. 354-359, 2017.

- [13] Thiyagarajan, V. and Somasundaram, P.: A New Seven Level Symmetrical Inverter with Reduced Switch Count. In: International Journal of Power Electronics and Drive System, vol. 9, no. 2, pp. 921-925, 2018.

- [14] Jayabalan, M., Jeevarathinam, B. and Sandirasegarane, T.: Reduced switch count pulse width modulated multilevel inverter. In. IET Power Electronics, vol. 10, no. 1, pp. 10-17, 2017.

- [15] Samadaei, E., Sheikholeslami, A., Gholamian, S. A. and Adabi, J.: A Square T-Type (ST-Type) Module for Asymmetrical Multilevel Inverters. In. IEEE Transactions on Power Electronics, vol. 33, no. 2, pp. 987-996, 2018.

- [16] Odeh, C. I., Obe, E. S. and Ojo, O.: *Topology for cascaded multilevel inverter*. In. IET Power Electronics, vol. 9, no. 5, pp. 921-929, 2016.

- [17] Thamizharasan, S., Baskaran, J., Ramkumar, S. and Jeevananthan, S.: Cross-switched multilevel inverter using auxiliary reverse-connected voltage sources. In. IET Power Electronics, vol. 7, no. 6, pp. 1519-1526, 2014.

- [18] Ajami, A., Oskuee, M. R. J., Mokhberdoran, A., and Van den Bossche, A.: Developed cascaded multilevel inverter topology to minimise the number of circuit devices and voltage stresses of switches. In. IET Power Electronics, vol. 7, no. 2, pp. 459-466, 2014.

- [19] Ajami, A., Mokhberdoran, A. and Oskuee, M. R. J.: A New Topology of Multilevel Voltage Source Inverter to Minimize the Number of Circuit Devices and Maximize the Number of Output Voltage Levels. In. Journal of Electr. Eng. Technol., vol. 8, no. 6, pp. 1328-1336, 2013.