# A Novel Integration of Three-Level AC–DC Converter with Closed Loop Controller

Mr V Jayanth Kumar<sup>1</sup>

Dr O.ChandraSekhar<sup>2</sup>

<sup>1</sup>P.G Student, K.L University, Green fields, vaddeswaram, Guntur, Andhra Pradesh, India,jayanthfun4all@hotmail.com <sup>2</sup>Professor, K.L University, Green fields, vaddeswaram, Guntur, Andhra Pradesh, India,sekhar.obbu@gmail.com

Abstract: In this project, closed loop integrated threelevel ac-dc converter is presented in order to improve the stability of the system. By implementation of PI controller with PWM technique in closed loop, the switching sequence is under controlled condition and the output voltage of the proposed converter effectively increases. Mainly the present converter is combination of the operation of boost power factor correction and threelevel dc-dc converter. Two large capacitors are taken in order to improve the efficiency and accuracy of the ac-dc converter. This converter operated with two different controllers. Power factor correction and regulation of dc bus voltage was done by input controller. The output voltage is maintained by output controller. In this we are using single stage converter topology in which the dc bus voltage in single stage converter is controlled by input controller. Finally in this project we are maintaining the stability of the previously implemented three-level integrated ac-dc converter. The flexibility of the improved converter is obtained from prototype which are shown in simulation results by using MATLAB/Simulink.

**Index Terms:** AC–DC power conversion, single-stage power factor correction (SSPFC), three-level converters.

## I. INTRODUCTION

For running industrial dries power electronic dries are much essential. High power and medium voltage requirements, drives are implemented in recent period. Limited Voltage and current ratings of a semiconductor can be overwhelmed by the means of series or parallel connection of drives. Multi-level inverters have become popular because of their capability to obtain waveforms with less harmonic distortion and achieve higher voltages. Transformer isolation is needed for ac-dc power supplies which

are developed with some kind of input Power factor correction to fulfil with standard of harmonics like IEC 1000-3-2.

Advancement is done in usage of power electronic converters which are manufactured in order to develop products with power factor correction. The essential requirement performance of power electronic converters are high power factor and currents with low input harmonics. Old rectifiers with passive diode or LC filter with input can be combined to fit by using filters with passive elements. Because of the size of Inductors and capacitors of low frequency, the converter is very huge and heavy. In order to obtain better power factor and reduction of harmonics. Active power factor correction techniques have been used in AC-DC converter. Active power factor correction can be classified into two stage scheme. Two stages PFC contain two independent power stages in cascade with PFC stage and DC-DC regulator. The total efficiency of the two stages is lower because the total power has to be processed twice with two cascade power stage. Cost of the circuit is increase several schemes have developed to combine stage into one stage.

The open loop control of a three level integrated ac-dc has very less output voltage. To regulate the excessive dc bus voltages, minimize the large output ripples, distorted input currents and for better output voltage there is a need for a converter, which overcomes all these drawbacks.

In this paper, a closed loop control of a single stage three level integrated ac-dc converter that does not have the drawbacks of previously proposed single-stage and two-stage converters is proposed.

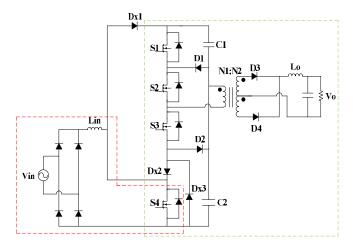

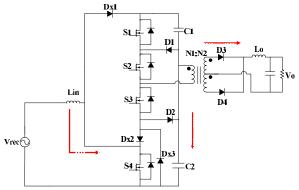

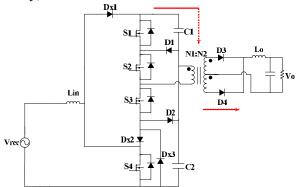

Fig.1.Single-stage three-level AC-DC converter in open loop condition

# II. OPERATION OF THE PROPOSED CONVERTER

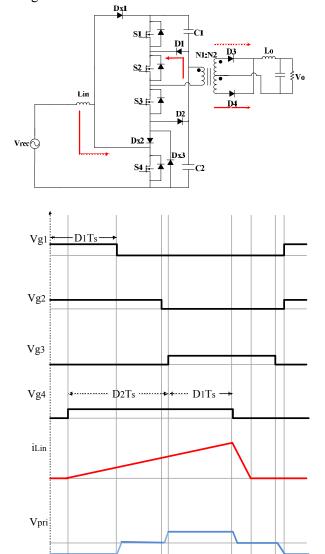

The implemented converter in open loop condition, as shown in Fig. 1, which mixes dc-dc converter three levelled fed by ac-dc boost Power Factor Correction converter. The ac-dc boost section consists of an input diode bridge, boost Inductor L<sub>in</sub>, boost diode  $D_{x1}$ , and switch  $S_4$ , which is shared by the multilevel dc-dc section. Boost inductor cannot collect any energy when S<sub>4</sub> turn off. In this case, diode D<sub>x2</sub> prevents input current from flowing to the midpoint of capacitors  $C_1$  and  $C_2$  and diode  $D_{x1}$ conducts and helps to transfer the energy stored in the boost inductor  $L_{\text{in}}$  to the dc bus capacitor. Diode  $D_{x3}$  bypasses  $D_{x2}$  and makes a path for circulating current. It contains a single converter which can be monitored with two controllers independently. Power Factor correction and voltage regulation across the dc-bus capacitors on the primary side by giving specific triggering signal to S<sub>4</sub> can be achieved by one controller. The output voltage regulation by giving specific triggering signals to S<sub>1</sub> to S<sub>4</sub> can be done by other controller. The section of input can be monitored which is separated from the control of section of dc-dc and thereby individually designed. The output of input controller can be found by triggering signal of S<sub>1</sub> which is based on S<sub>4</sub>, the generation of this signal can be discussed clearly in this project in coming section. When both switches are turn ON for half a switching cycle which are not at same time, then obtaining triggering signals for S<sub>2</sub> and S<sub>3</sub> are simple. In Fig.2 and Fig.3 the waveforms of converter and the diagrams of similar circuit which show the stages of operation of converter with the resultant bridge diode rectifier fed by sinusoidal source which is rectified as shown. The supply voltage is assumed and remained same only when the input line frequency is much lower than the switching frequency. Eventhough the input current is made discontinuous which is not desired but the input current can be made continuous. The different stages of operation of converter are given below.

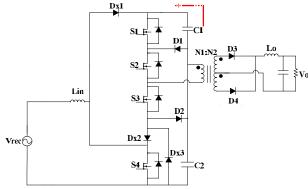

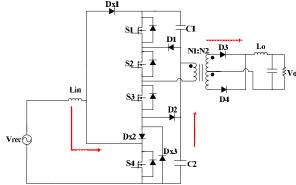

1) Mode 1 ( $t_0 \le t \le t_1$ ): During this mode, the output load is energized by the discharge of dc-bus capacitor  $C_1$  by turn ON of switches  $S_1$  and  $S_2$ . The positive voltage on the output side of transformer is given across Lo which makes current rising.

2) Mode 2 ( $t_1 \le t \le t_2$ ): During this mode, the output load is energized by the discharge of dc-bus capacitor  $C_1$  by making  $S_1$  and  $S_2$  still Turn ON and S3 turns ON and also the output voltage of the diode bridge rectifier is given across the input inductor Lin thereby inductor current rising.

3) Mode3 ( $t_2 \le t \le t_3$ ): In this mode, the switches  $S_1$  and  $S_2$  are still Turn ON and  $S_3$  turns ON. The output load is energized by discharging of dc-bus capacitor  $C_1$ . The output voltage of diode bridge rectifier is applied across input inductor Lin in order to make

the inductor current which raises voltage applied across input inductor Lin thereby inductor current rising.

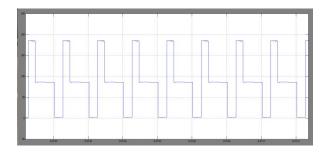

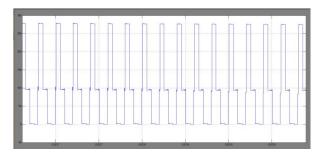

Fig. 2. Typical waveforms describing the modes of operation.

t3 t4

t7 t8

t2

iLo

to t1

4) Mode 4 ( $t_3 \le t \le t_4$ ): During this mode, the switches  $S_1$  and  $S_2$  are turn OFF and  $S_4$  is turn ON such that the capacitor  $C_2$  is charged by the primary current of the transformer through the body diode of switch  $S_3$  and diode  $D_{x3}$ .

5) Mode 5 ( $t_4 \le t \le t_5$ ): In this mode,  $S_3$  and  $S_4$  are ON. Energy flows from capacitor  $C_2$  flows into the load while the current flowing through input inductor  $L_{in}$  continues to rise.

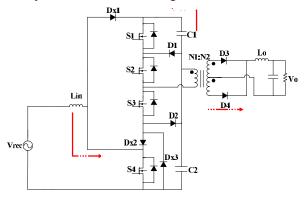

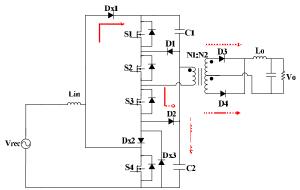

6) Mode 6 ( $t_5 \le t \le t_6$ ): In this mode,  $S_4$  turns off. The current in input inductor flows thorough the diodeD<sub>x1</sub> to charge the capacitors  $C_1$  and  $C_2$ . The current in the transformer primary flows thorough the  $S_3$  and  $D_2$ . This mode ends when the inductor current reaches zero. Also during this mode, the load inductor current freewheels in the secondary of the transformer.

7) Mode 7 ( $t_6 \le t \le t_7$ ): In this mode, the load inductor current freewheels in the secondary of the transformer. This mode ends when the switches  $S_3$ turns off.

8) Mode 8 ( $t_7 \le t \le t_8$ ): In this mode,  $S_3$  is OFF and the current in the primary of the transformer charges capacitor  $C_1$  through the body diodes of  $S_1$  and  $S_2$ . Finally, converter reenters Mode 1.

# III. CONTROL STRATEGY AND CONVERTER DESIGN

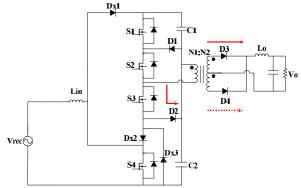

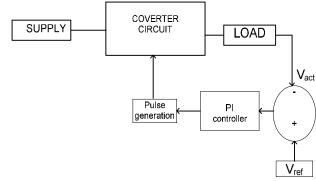

This section mainly focused on the control technique for the Single stage three level controllers. Closed loop PI controller with PWM technique gives the better performance as compared with the conventional converter. The block diagram of the proposed control technique is shown in Fig 3.

PI controller receives output voltage as input signal. Based on the input signal the PI controller generates a reference dc voltage signal which is an input signal to PWM generator. The values of PI controller gains (i.e. Integral gain and proportional gain) are tuned in order to attain better output voltage. The PWM generator compares the dc reference signal with the saw tooth carrier signal and generates the pulses.

Fig.3. Block diagram of proposed system

A procedure for the design of the converter is presented in this section and is demonstrated with an example. The converter is to be designed with the following parameters for the example:

- 1) input voltage: Vin = 90–265 Vrms;

- 2) output voltage: Vo = 48 V;

- 3) maximum output power: Po = 1350 W;

- 4) switching frequency: fsw=1/TSW = 50 kHz;

- 5) input current harmonics: IEC1000-3-2 for Class D electrical equipment.

A. Step 1: Determine Value for Output Inductor Lo

The output inductor should be designed so that the

output current is made to be continuous under most

operating conditions. The minimum value of Lo

should be the value of Lo with which the converter's

output current will be continuous on the when the

converter is operating with maximum input voltage,

minimum duty cycle (Dmin), and at least 50% of

maximum load. The minimum value of Lo can,

therefore, be determined to be

$$Lo, max \ge \frac{Vo^2}{0.5 Po, max} \frac{1-Dm}{2} \frac{Tsw}{2}. \tag{1}$$

Substituting Po, max = 1350 W, Vo = 48 V,  $TSW = 20 \mu s$ , and Dm = 0.45 gives Lo, min  $\geq 9.36 \mu H$  and the value of Lo should be larger to provide some margin. It should be noted that such a value is considerably higher than what is typically found in most other single-stage full-bridge converters, which must operate with very low output inductor values to prevent the dc-bus voltage from becoming excessive. A value of  $Lo = 10 \mu H$ , which is just above  $9.36 \mu H$ , is chosen.

B. Step 2: Determine Value for Turns Ratio of Main Transformer N

The relation between Vbus, D, Vo and N is

$$Vo = \frac{Vbus}{2N}D$$

(2)

The minimum value of N can be found by considering the case when the converter must operate with minimum input line and, thus, minimum primary-side dc-bus voltage *V*bus,min and maximum duty cycle Dmax.

$$N \ge \frac{Vbus_{min}}{2Vo}$$

. Dmax (3)

Vbus = 650 V and it is achieved by controlling the S4. Substituting Vo = 48 and Dmax = 0.75, then the value of N should be equal or more than 5. In this example, the value of transformer ratio is considered to be equal to N = 5.

C. Step 3: Determine Value for Inductor Lin

The value for Lin should be low enough to ensure

that the input current is fully discontinuous under all

operating conditions, but not so low as to result in

excessively high peak current. For the case where

Lin is such that the input current remains

discontinuous for all operating conditions, the

minimum value of Lin determine as

$$Lin, max < \frac{[(Vbus, min)]^2 * Dmax * (1 Dmax)^2}{2Fo, \max fsw}$$

(4)

Where Dmax = 0.75, V bus,min = 650 V, Po,max = 1.35 kW, and fSW = 50 kHz. The minimum value of Lin = 114  $\mu$ H is found. For this design, Lin = 80  $\mu$ H is used one controller is used to control dc-bus voltage and shape the input current and one controller for control output voltage. The time constant for PFC controller should be faster in compare to output voltage controller.

## IV.CONVERTER FEATURES

The proposed converter has the following features:

A. Reduced cost compared to two-stage converters: Although the proposed converter may seem expensive, the reality is that it can be cheaper than a conventional two-stage converter. This is because replacing a switch and its associated gate drive

circuitry with four diodes reduces cost considerably even though the component count seems to be increased—this is especially true if the diodes are ordered in bulk numbers.

B. Better performance than a single-stage converter: The proposed single-stage converter can operate with a better input power factor for universal input line applications than a single-controller, single-stage because it does have a dedicated controller for its input section that can perform PFC and regulate the dc-bus voltage. The presence of a second controller also allows the converter to operate with better efficiency and with less output ripple as each section.

#### C. Improved Light-Load Efficiency:

The proposed converter can be designed so that it has a conventional dc-bus voltage of 400 V. Since the converter is a multilevel converter, a 400 V dc bus means that each switch will be exposed to a maximum voltage of 200 V. Having 200 V across a MOSFET device instead of 400 V (as is the case with two-level converters) results in a 75% reduction in turn on losses when the converter is operating under light-load conditions and there is an insufficient amount to current available to discharge the switch output capacitances before the switches are turned on.

#### D. Increased Design Flexibility:

Since the converter is a multilevel converter, it can be operated with high dc-bus voltage (800 V), standard dc-bus voltage (400 V), or any dc-bus voltage 400 V<Vbus<800 V. There are advantages to operating with high dc-bus voltage or with standard dc bus voltage. The fact there is flexibility in the level that the dc-bus voltage is set means that there is considerable flexibility in the design of the converter. This gives the designer options as to how to optimize the design of the converter for other factors such as efficiency profile and cost (i.e. cost of switches based on voltage rating considerations and availability). It should be noted that this design flexibility makes the design of the three-level converter to be much simpler than that of a singlestage two-level converter or that of a singlecontroller three-level single stage converter as the dc-bus voltage can be fixed to a desired level that is considered appropriate. It should be noted that although the proposed converter has aforementioned advantages over the conventional two-stage converter, it will have lower heavy-load efficiency because of increased conduction losses as switch S4 must conduct both the input current and the full-bridge current. As a result, when determining whether to use the proposed converter versus a conventional two-stage converter, the main trade off that needs to be considered is lower cost and improved light-load efficiency versus heavyload efficiency.

# V. MATLAB/SIMULINK RESULTS

Case i: Single-Stage Three-Level Converter Under open loop condition.

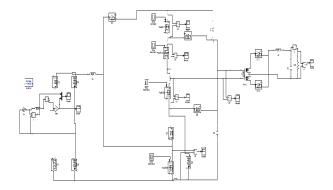

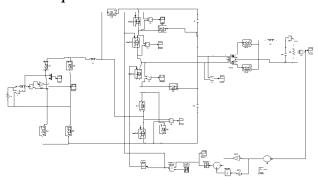

Fig.4:Matlab/Simulink circuit of Single-Stage Three-Level Converter in open loop condition.

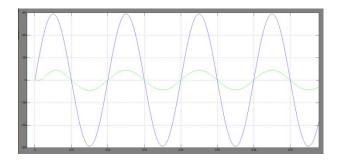

Fig.5: Input Current and Voltage Wave Forms

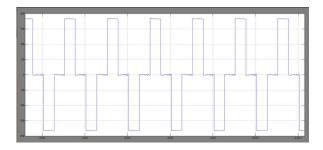

Fig.6: Voltage across Switch S1

Fig.7: Voltage across Switch S2

Fig.8: Voltage across Switch S3

Fig.9: Voltage across Switch S4

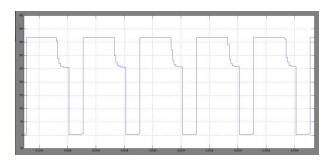

Fig. 10: Three Level Output Voltage at primery side of transformer

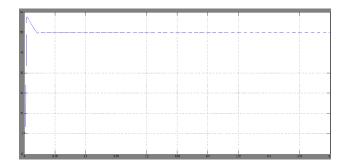

Fig.11: Output Voltage

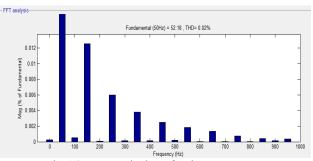

Fig.12. FFT window for input current

# Case ii: Single-Stage Three-Level Converter Under closed loop condition

Fig.4:Matlab/Simulink circuit of Single-Stage Three-Level Converter in closed loop condition.

Fig.11: Output Voltage

Fig.12. FFT window for input current

## **VI.CONCLUSION**

A closed loop control of a three level integrated ac-dc converter is proposed in the paper. This converter is operated with two controllers, one controller that performs input PFC and a second controller that regulates the output voltage. The outstanding feature of this converter is that it combines the performance of two-stage converters with the reduction of cost of single-stage converters. By using PI controller with PWM technique in the switching sequence is under loop, controlled condition. Hence the proposed converter output dc voltage is effectively increased. Efficiency of the proposed converter is also comparatively more. For high dc voltage requirements this proposed converter is efficient.

The paper introduces the proposed converter, explains its basic operating principles and modes of operation, and discusses its design with respect to different dc-bus voltages.

## REFERENCES

- [1] J.-Y. Lee, "Single-stage AC/DC converter with input-current dead-zone control for wide input voltage ranges," IEEE Trans. Ind. Electron., vol. 54, no. 2, pp. 724–732, Apr. 2007.

- [2] D. D.-C. Lu, H. H.-C. Iu, and V. Pjevalica, "A single-stage AC/DC converter with high power factor, regulated bus voltage, and output voltage," IEEE Trans. Power Electron., vol. 23, no. 1, pp. 218–228, Jan. 2008.

- [3] H. Ma, Y. Ji, and Y. Xu, "Design and analysis of single-stage power factor correction converter with a feedback winding," IEEE Trans. Power Electron., vol. 25, no. 6, pp. 1460–1470, Jun. 2010.

- [4] H. S. Athab and D. D.-C. Lu, "A high-efficiency ac/dc converter with quasi-active power factor correction," IEEE Trans. Power Electron., vol. 25, no. 5, p. 1103-1109, May 2010.

- [5] J. M. Kwon, W. Y. Choi, and B. H. Kwon, "Single-stage quasi-resonant fly back converter for a cost-effective PDP sustain power module," IEEE Trans. Ind. Electron., vol. 58, no. 6, pp. 2372–2377, Jun. 2011.

- [6] H. J. Chiu, Y. K. Lo, H. C. Lee, S. J. Cheng, Y. C. Yan, C. Y. Lin, T. H. Wang, and S. C. Mou, "A single-stage soft-switching fly back converter for power-factor-correction applications," IEEE Trans. Ind. Electron., vol. 57, no. 6, pp. 2187–2190, Jun. 2011.

- [7] H. Athab and D. Lu, "A single-switch ac/dc fly back converter using a CCM/DCM quasi-active power factor correction front-end," IEEE Trans. Ind. Electron., vol. 59, no. 3, pp. 1517–1526, Mar. 2012.

- [8] N. Golbon and G. Moschopoulos, "A low-power acde single-stage converter with reduced dc bus voltage variation," IEEE Trans. Power Electron., vol. 27, no. 8, pp. 3714–3724, Jan. 2012.

- [9] P. K. Jain, J. R. Espinoza, and N. Ismail, "A single-stage zero-voltage zero-current-switched full-bridge DC power supply with extended load power range," IEEE Trans. Ind. Electron., vol. 46, no. 2, pp. 261–270, Apr. 1999

- [10] G. Moschopoulos, "A simple AC–DC PWM full-bridge converter with integrated power-factor correction," IEEE Trans. Ind. Electron., vol. 50, no. 6, pp. 1290–1297, Dec. 2003.

- [11] G. Moschopoulos, Q. Mei, H. Pinheiro, and P. Jain, "PWM full-bridge converter with natural input power factor correction," IEEE Trans. Aerosp. Electron. Syst., vol. 39, no. 2, pp. 660–674, Apr. 2003.

- [12] P. Das, S. Li, and G. Moschopoulos, "An improved AC–DC single-stage full-bridge converter with reduced DC bus voltage," IEEE Trans. Ind. Electron., vol. 56, no. 12, pp. 4882–4893, Dec. 2009.

- [13] M. S. Agamy and P. K. Jain, "A three-level resonant single-stage power factor correction converter: analysis, design, and implementation industrial electronics," IEEE

- Trans. Ind. Electron., vol. 56, no. 6, pp. 2095–2107, Jun. 2009.

- [14] H. L. Cheng, Y. C. Hsieh, and C. S. Lin, "A novel single-stage high power factor ac/dc converter featuring high circuit efficiency," IEEE Trans.Ind. Electron., vol. 58, no. 2, pp. 524–532, Feb. 2011.

- [15] M. S. Agamy and P. K. Jain, "A variable frequency phase-shift modulated three-level resonant single-stage power factor correction converter," IEEE Trans. Power Electron., vol. 23, no. 5, pp. 2290–2300, Sep. 2009.