# A REDUCED SWITCH COUNT ASYMMETRICAL THREE PHASE MULTILEVEL INVERTER TOPOLOGY

# Anbarsan,P1; Ramkumar,S2 & Thamizharasan,S3

<sup>1</sup> St.Joseph's College of Engineering, OMR, Chennai, TN, India <sup>2</sup>KPR Institute of Engineering and Technology, Coimbatore, TN, India <sup>3</sup> Saranathan College of Engineering, Trichy, TN, India E-Mail: <sup>1</sup>anbarasan\_3e@yahoo.co.in, <sup>2</sup> ramme04@gmail.com, <sup>3</sup>thamizharsan.s@gmail.com

**Abstract:** A novel multilevel inverter topology for three-phase medium-voltage high power applications is proposed in this paper with a perspective to offer reduced number of power components. The topology is formulated using series connection of several fundamental inverter blocks. The fundamental block is constituted with two dc sources and six bidirectional switches by operating the topology in asymmetrical dc voltages to produce seven level output. The proposed multilevel inverter has the advantage of minimal switches in each conduction path. The simulation results are shown to prove the effectiveness of the proposed topology.

**Key words:** Multilevel inverter, Asymmetrical, Operating modes, Pulse width modulation, Switch count.

#### 1. Introduction

The multilevel inverter becomes one of the most considerable power electronic devices for synthesizing the output voltage to suit specific application. Their competence leads to apply in high voltage aspect without affecting the voltage limit capability of power devices. This behavioral qualities benefit in good power quality, high voltage blocking capability and less EMI [1]. The first MLI structure is neutral point clamped inverter [2] which employs a series of capacitor banks to segregate the dc link voltages and succeed to voltage unbalance problems. The series of H-bridge cells are connected to synthesize stair case voltage is Cascaded H-bridge MLI which also suffers a major drawbacks of excessive H-bridge cell for higher voltage levels and each H-bridge requires multiwinding transformers [3]. The next conventional MLI is flying capacitor MLI which uses floating capacitors to clamp the voltage levels and also suffers voltage balancing problems [4]. A new multilevel inverter with a chain of dc sources arranged in cross fashion to synthesize the multilevel waveform and however the topology requires higher number of power components in its conduction path and devices with high blocking voltages [5]. A symmetric multilevel inverter using non insulated dc sources have been proposed with a view to defend reduced number of switching devices compared to conventional inverters and it has a problem of utilizing large number of bidirectional devices, an Hbridge inverter with high blocking voltages for polarity reversal and bulky high frequency transformers [6]. A dual dc source intertied with half bridge cells based multilevel inverter is proposed in [7] to produce multilevel waveform. The topology requires bulkier transformer to synthesize three phase waveform and control is complex. A hybrid multilevel inverter employing half bridge cells at each phase leg of six switch inverter is presented in [8] and the topology has circulating energy problems. A phase leg of back to back dc sources connected through six switches is addressed in [9] to offer less number of power components in multilevel inverter topologies. The topology requires switching devices with high blocking voltage which is equal to sum of dc sources. Several remarkable attempts have been made to add a boost to the innovations in multilevel topologies [10-15]. In this paper, an innovative idea in the area of three phase multilevel inverter topologies has been suggested. The detailed operation of the proposed topology is explained in section 2. The power loss analysis and comparison between the proposed and classical topologies have been addressed in section 3. Following simulation results are portrayed to corroborate the viability of the proposed inverter in medium voltage/high power applications.

# 2. Proposed Topology

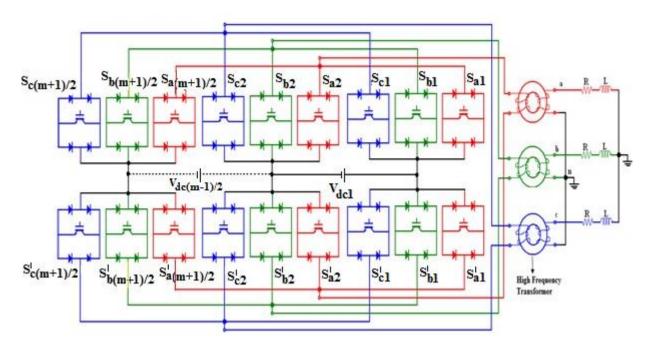

The Fig.1 depicts the proposed three phase topology using series connected isolated dc sources, switching devices and high frequency transformers. The proposed topology is extended to any number of voltage levels with generalized dc sources as  $(V_{dc1} - V_{dc(m-1/2)})$  and switching devices as  $(S_{a1} - S_{a(m+1/2)}, S_{a1}' - S_{a(m+1/2)})$ . The Table I illustrates switching sequence to drag the level magnitude in each phase per fundamental cycle.

Fig. 1 Generalized structure of the proposed topology

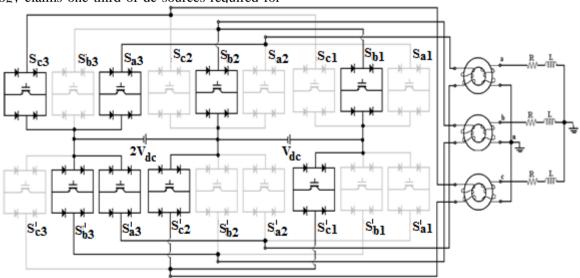

For instance, the switches ( $S_{a3}$ ,  $S_{a3}$ '), ( $S_{b1}$ ,  $S_{b2}$ ,  $S_{b3}$ ) and ( $S_{c1}$ ',  $S_{c2}$ ',  $S_{c3}$ ) are triggered to generate  $V_{an}$  =0,  $V_{bn}$  = -3 $V_{dc}$  and  $V_{cn}$  = 3 $V_{dc}$  and portrayed in Fig.2. The proposed three phase topology makes use of unequal DC sources and comes under the category of asymmetrical topology. The magnitudes of the dc sources are arranged in the factor of 2 produces (4n-1) and (8n-3) level in phase and line voltages respectively. The maximum output voltage for this proposed topology in asymmetric configuration is given by (2n-1)× $V_{dc}$ . The entries in Table 1 and 2 portray the comparison between the proposed, conventional and recent topologies. It is inferred that the proposed topology claims one third of dc sources required for

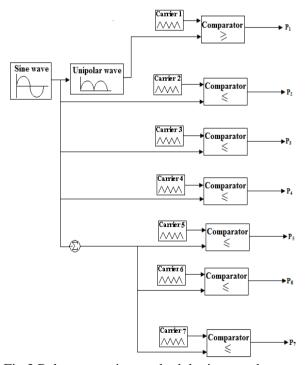

conventional topologies and switching devices in the conduction path while increasing the number of levels. Table 3 compares the power component required between symmetrical and asymmetrical configuration of the proposed topology. The comparisons of power components between proposed and other topologies for m level are presented in Table 4. The multicarrier PD-pulse width modulation generation shown in Fig.3 is used to buffer the switches in the proposed topology and the corresponding logical operation is tabulated in Table 5.

Fig. 2 Seven level inverter with mode diagram for  $V_{an} = 0$ ,  $V_{bn} = -3V_{dc}$  and  $V_{cn} = +3V_{dc}$

Table 1 Asymmetrical Operating modes per cycle

| Modes | Output          | Phase V    | oltages         | Conducting Switches                         |                                             |                                           |

|-------|-----------------|------------|-----------------|---------------------------------------------|---------------------------------------------|-------------------------------------------|

|       | V <sub>an</sub> | $V_{bn}$   | V <sub>cn</sub> | V <sub>an</sub>                             | $V_{bn}$                                    | $V_{cn}$                                  |

| 1     | 0               | $-3V_{dc}$ | $3V_{dc}$       | $S_{a3}$ , $S_{a3}$                         | $S_{b1}$ , $S_{b2}$ , $S_{b3}$              | $S_{c1}', S_{c2}', S_{c3}$                |

| 2     | $V_{dc}$        | $-3V_{dc}$ | $3V_{dc}$       | $S_{a1}$ ', $S_{a2}$ , $S_{a3}$             | $S_{b1}$ , $S_{b2}$ , $S_{b3}$              | $S_{c1}', S_{c2}', S_{c3}$                |

| 3     | $V_{dc}$        | $-3V_{dc}$ | $2V_{dc}$       | $S_{a1}$ , $S_{a2}$ , $S_{a3}$              | $S_{b1}$ , $S_{b2}$ , $S_{b3}$              | $S_{c1}', S_{c2}, S_{c2}', S_{c3}$        |

| 4     | $2V_{dc}$       | $-3V_{dc}$ | $2V_{dc}$       | $S_{a1}$ ', $S_{a2}$ , $S_{a2}$ ', $S_{a3}$ | $S_{b1}$ , $S_{b2}$ , $S_{b3}$              | $S_{c1}', S_{c2}, S_{c2}', S_{c3}$        |

| 5     | $2V_{dc}$       | $-3V_{dc}$ | $V_{dc}$        | $S_{a1}$ ', $S_{a2}$ , $S_{a2}$ ', $S_{a3}$ | $S_{b1}$ , $S_{b2}$ , $S_{b3}$              | $S_{c1}', S_{c2}, S_{c3}$                 |

| 6     | $3V_{dc}$       | $-3V_{dc}$ | $V_{dc}$        | $S_{a1}$ ', $S_{a2}$ ', $S_{a3}$            | $S_{b1}$ , $S_{b2}$ , $S_{b3}$              | $S_{c1}', S_{c2}, S_{c3}$                 |

| 7     | $3V_{dc}$       | $-3V_{dc}$ | 0               | $S_{a1}$ ', $S_{a2}$ ', $S_{a3}$            | $S_{b1}$ , $S_{b2}$ , $S_{b3}$              | $S_{c3}$ , $S_{c3}$                       |

| 8     | $3V_{dc}$       | $-3V_{dc}$ | $-V_{dc}$       | $S_{a1}$ ', $S_{a2}$ ', $S_{a3}$            | $S_{b1}$ , $S_{b2}$ , $S_{b3}$              | $S_{c1}$ , $S_{c2}$ , $S_{c3}$ , $S_{c3}$ |

| 9     | $3V_{dc}$       | $-2V_{dc}$ | $-V_{dc}$       | $S_{a1}$ ', $S_{a2}$ ', $S_{a3}$            | $S_{b1}$ , $S_{b2}$ , $S_{b2}$ , $S_{b3}$ , | $S_{c1}$ , $S_{c2}$ , $S_{c3}$ , $S_{c3}$ |

| 10    | $3V_{dc}$       | $-2V_{dc}$ | $-2V_{dc}$      | $S_{a1}$ ', $S_{a2}$ ', $S_{a3}$            | $S_{b1}$ , $S_{b2}$ , $S_{b2}$ , $S_{b3}$   | $S_{c1}$ , $S_{c2}$ , $S_{c2}$ , $S_{c3}$ |

| 11    | $3V_{dc}$       | $-V_{dc}$  | $-2V_{dc}$      | $S_{a1}$ ', $S_{a2}$ ', $S_{a3}$            | $S_{b1}$ , $S_{b2}$ , $S_{b3}$ , $S_{b3}$   | $S_{c1}$ , $S_{c2}$ , $S_{c2}$ , $S_{c3}$ |

| 12    | $3V_{dc}$       | $-V_{dc}$  | $-3V_{dc}$      | $S_{a1}$ ', $S_{a2}$ ', $S_{a3}$            | $S_{b1}$ , $S_{b2}$ , $S_{b3}$ , $S_{b3}$   | $S_{c1}, S_{c2}, S_{c3}$                  |

| 13    | $3V_{dc}$       | 0          | $-3V_{dc}$      | $S_{a1}$ ', $S_{a2}$ ', $S_{a3}$            | $S_{b3}$ , $S_{b3}$ '                       | $S_{c1} , S_{c2} , S_{c3} $               |

| 14    | $3V_{dc}$       | $V_{dc}$   | $-3V_{dc}$      | $S_{a1}$ ', $S_{a2}$ ', $S_{a3}$            | $S_{b1}$ , $S_{b2}$ , $S_{b3}$              | $S_{c1} , S_{c2} , S_{c3} $               |

| 15    | $2V_{dc}$       | $V_{dc}$   | $-3V_{dc}$      | $S_{a1}$ ', $S_{a2}$ , $S_{a2}$ ', $S_{a3}$ | $S_{b1}', S_{b2}, S_{b3}$                   | $S_{c1} , S_{c2} , S_{c3}$                |

| 16    | $2V_{dc}$       | $2V_{dc}$  | $-3V_{dc}$      | $S_{a1}$ ', $S_{a2}$ , $S_{a2}$ ', $S_{a3}$ | $S_{b1}', S_{b2}, S_{b3}$                   | $S_{c1} , S_{c2} , S_{c3}$                |

| 17    | $V_{dc}$        | $3V_{dc}$  | $-3V_{dc}$      | $S_{a1}$ ', $S_{a2}$ , $S_{a3}$             | $S_{b1}', S_{b2}', S_{b3}$                  | $S_{c1}$ , $S_{c2}$ , $S_{c3}$            |

| 18    | $V_{dc}$        | $3V_{dc}$  | $-3V_{dc}$      | $S_{a1}$ ', $S_{a2}$ , $S_{a3}$             | $S_{b1}$ ', $S_{b2}$ ', $S_{b3}$            | $S_{c1}$ , $S_{c2}$ , $S_{c3}$            |

Table 2 Comparison between proposed and conventional topologies for 'm' level

| Multilevel<br>inverter<br>structure | Cascaded<br>H-bridge | Diode<br>clamped<br>(1981) | Flying<br>Capacitor | Proposed |

|-------------------------------------|----------------------|----------------------------|---------------------|----------|

| Main switches                       | 6(m-1)               | 6(m-1)                     | 6(m-1)              | (m+5)/2  |

| Bypass diodes                       | -                    | -                          | -                   | -        |

| Clamping diodes                     | -                    | 6(m-3)                     | -                   | -        |

| DC split capacitors                 | -                    | 3(m-1)/2                   | 3(m-1)/2            | -        |

| Clamping capacitors                 | -                    | -                          | 3(2m-6)/2           | -        |

| DC sources                          | 3(m-1)/2             | 1                          | 1                   | (m-1)/2  |

Table 4 Comparison between proposed and similar topologies for 'm' level

| Multilevel<br>inverter<br>structure   | Diode bypassed dc-<br>link inverter | Diode bypass neutral point inverter | SPSMLDCLI | Cross switched<br>MLI | Proposed |

|---------------------------------------|-------------------------------------|-------------------------------------|-----------|-----------------------|----------|

| Main switches                         | 3(m+7)/2                            | 3(m+1)                              | 3(3m-1)/2 | 3(m+3)                | (m+5)/2  |

| Bypass diodes                         | 3(m-1)/2                            | 3(m-1)/2                            | 3         | -                     | -        |

| Clamping diodes                       | =                                   | =                                   | 1         | -                     | -        |

| DC split capacitors                   | =                                   | -                                   | ı         | -                     | -        |

| Clamping capacitors                   | =                                   | =                                   | ı         | -                     | -        |

| No. of devices in the conduction path | 3(m+3)/2                            | 3(m+1)/2                            | 3(m-1)    | 3(m+3)/2              | 2        |

| DC sources                            | 3(m-1)/2                            | 3(m-1)/2                            | 3(m-1)/2  | 3(m-1)/2              | (m-1)/2  |

Table 3 Comparison of power components required for proposed inverters

|                                                                                                                 | proposed          |                                |

|-----------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------|

| Parameters                                                                                                      | Symmetrical       | Asymmetrical                   |

| No. of DC<br>sources                                                                                            | n                 | N                              |

| No. of switches                                                                                                 | 2n+2              | 2n+2                           |

| No. of output levels                                                                                            | (2×n)+1           | (4×n)-1                        |

| Maximum<br>voltage                                                                                              | $n\times V_{dc}$  | $((2\times n)-1)\times V_{dc}$ |

| Standing voltages on all the switches (S <sub>1</sub> -S <sub>n</sub> ) and (S <sub>1</sub> '-S <sub>n</sub> ') | $n \times V_{dc}$ | ((2×n)-1)×V <sub>dc</sub>      |

Table 5 Digital process of control signals

| Switches          | Control Signals                                                              |

|-------------------|------------------------------------------------------------------------------|

| $S_{a1}$          | (P <sub>5</sub> XOR P <sub>6</sub> ) OR P <sub>7</sub>                       |

| S <sub>a1</sub> ' | (P <sub>2</sub> XOR P <sub>3</sub> ) OR P <sub>4</sub>                       |

| $S_{a2}$          | (P <sub>2</sub> XOR P <sub>3</sub> ) OR (P <sub>6</sub> XOR P <sub>7</sub> ) |

| S <sub>a2</sub> ' | (P <sub>3</sub> XOR P <sub>4</sub> ) OR (P <sub>5</sub> XOR P <sub>6</sub> ) |

| S <sub>a3</sub>   | P <sub>1</sub> OR P <sub>4</sub> OR (P <sub>3</sub> XOR P <sub>4</sub> )     |

| S <sub>a3</sub> ' | P <sub>1</sub> OR P <sub>7</sub> OR (P <sub>6</sub> XOR P <sub>7</sub> )     |

Fig.3 Pulse generation methodologies per phase.

## 3. Power loss analysis and comparison graph

The energy lost during turn-on and turn-off interval

of a switch is considered to compute the switching loss of the proposed topology. To simply the analysis, it is assumed that the voltage and current of a switch during switching varies linearly. Using this approximation, the energy lost during every turn-on and turn-off period of a switch can be obtained as

$$E_{on} = \frac{1}{6} V_{sw} I t_{on}$$

$$E_{toff} = \frac{1}{6} V_{sw} I t_{off}$$

where  $E_{on}$  and  $E_{off}$  are the energy lost during turnon and turn-off period of a switch and  $t_{on}$  and  $t_{off}$  are the turn-on and turn-off time of the switch.  $V_{sw}$  and I are voltage on and current through the switch before turning on or after turning off. For the multilevel inverter, the switching power loss can be computed as follows

$$P_{sw} = \frac{1}{T}(N_{on}E_{on} + N_{off}E_{off})$$

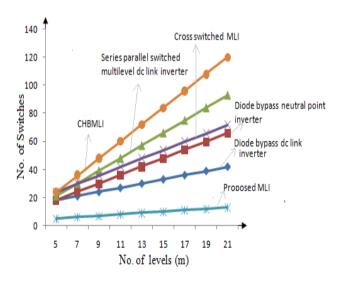

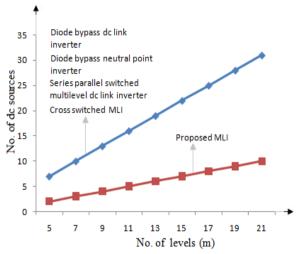

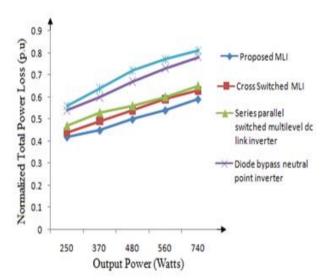

Where T is a fundamental cycle and ( $N_{on}$  and  $N_{off}$ ) is the number of times that the switches are turned on and off respectively. The total power loss of the switches can be obtained by adding the conduction and switching losses as shown in Fig. 4. The proposed topology offers lesser power loss in each switching devices compared to other topologies. Fig.5 shows the number of switch count versus voltage levels. The proposed asymmetrical configuration shows the greater enhancement in the number of levels. The comparison of number of dc sources versus voltage levels is shown in Fig.6

Fig.4 Comparison of switch count against voltage levels.

Fig.5 Comparison of dc sources required against voltage levels.

Fig.6 Comparison of total power loss against output power.

## 4. Simulation Results

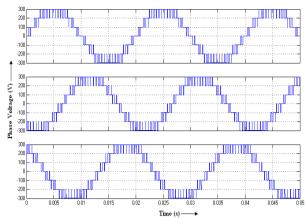

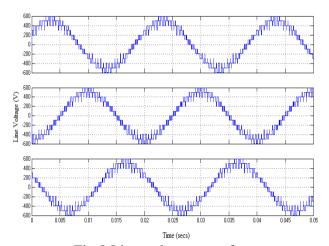

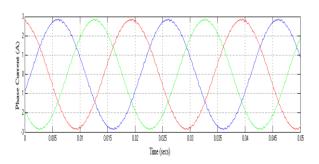

The proposed topology is simulated for seven level output in Matlab R2013b with simulation specifications:  $V_{dc1}$ = 100V,  $V_{dc2}$ = 200V, switching frequency of 2 kHz and star connected RL load of 150 $\Omega$  and 106mH in each phase respectively. The PWM required to trigger the switches using the methodology shown in Fig. 3. The simulated three phase voltage waveform ( $V_{AN}$ ,  $V_{BN}$  and  $V_{CN}$ ) are shown in Fig. 7. The corresponding line voltage waveform ( $V_{AB}$ ,  $V_{BC}$  and  $V_{CA}$ ) along with phase current waveform are depicted in Figs. 8 and 9 respectively

Fig.7 Phase voltage waveform.

Fig.8 Line voltage waveform.

Fig.9 Phase current waveform.

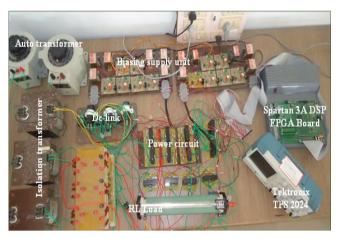

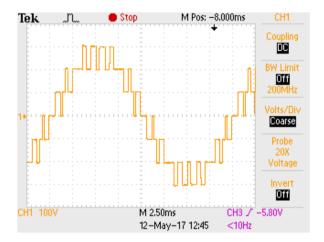

### 5. Harware Result

The seven level inverter is constructed for per phase and its prototype set up is shown in fig. The switching pulses are generated using Xilinx Spartan- 3A/3A FPGA controller. The fig depicts the phase voltage waveform of asymmetrical configurations. The experimental results shows the feasibility of the topology with simulation results and its usage in practical circuits and forge a new dimension for the use of MLIs.

Fig.10 Hardware setup

Fig.11 Output Voltage waveform for per phase

#### 5. Conclusion

A new three phase asymmetrical multilevel inverter topology has been proposed with an objective to offer reduced number of dc sources and switching devices for a given number of levels. The proposed has the advantage of only two switches conducting in each level transition of output voltage and has lesser power loss. The performance of the proposed topology is proven through simulation and analytical studies

#### References

- [1] Lai, JS & Peng, FZ 1996, 'Multilevel converters—a new breed of power converters,' IEEE Transaction on Industrial Application, vol. 32, pp. 509–517.

- [2] Nabae, A, Takahashi, I & Akagi, H 1981, 'A new neutral-point-clamped PWM inverter,' IEEE Transaction on Industrial Application, vol. 17, no. 5, pp. 518–523.

- [3] Malinowski, M., Gopakumar, K., Rodriguez, J., *et al.*: 'A survey on Cascaded Multilevel Inverters', *IEEE Trans. on Ind. Elec.*, 2010, **57**, (7), pp.2197-2206

- [4] Meynard, TA & Foch, H 1992, 'Multi-level choppers for high voltage applications,' in Proc. European Conf. Power Electronics and Applications, pp. 45–50.

- [5] Ajami, A., Jannati Oskuee, M.R., Mokhberdoran, A., et al.: 'Developed cascaded multilevel inverter topology to minimise the number of circuit devices and voltage stresses of switches' *IET Power Electronics*, 2014, **7**, (2), pp.459-466 5

- [6] Jamaludin, J., Rahim, N.A., Ping, H.W.: 'Multilevel voltage source inverter with optimized usage of bidirectional switches' *IET Power Electronics*, 2015, **8**, (3), pp.378-390

- [7] Kangarlu, MF & Babaei, E 2013b, 'A Generalized Cascaded Multilevel Inverter Using Series Connection of Submultilevel Inverters' IEEE transactions on power electronics, vol. 28, no. 2, pp. 625-636.

- [8] Veenstra, M & Rufer, A 2005, 'Control of a hybrid asymmetric multilevel inverter for competitive medium-voltage industrial drives,' IEEE Transaction on Industrial Application, vol. 41, no. 2, pp. 655–664.

- [9] Suresh, Y & Panda, AK 2012, 'Research on a cascaded multilevel inverter by employing three phase transformers,' IET Power Electronics, vol. 5, no. 5, pp. 561–570.

- [10] Arif Al-Judi and Edwin Nowicki, 2013, 'Cascading of diode bypassed transistor voltage source units in multilevel inverters', IET Power Electronics, vol.6, n0.3,pp.554-560.

- [11] Thamizharasan, S, Baskaran, J, Ramkumar, S & Jeevananthan, S, 2014, 'Cross switched multilevel inverter using auxiliary reverse-connected voltage sources' IET Power Electronics, vol. 7, no. 6, pp. 1519-1526.

- [12] Ramkumar, S., Kamaraj, V., Thamizharasan, S., *et al.*: 'A new series parallel switched multilevel dc-link inverter topology', Int. J. Elect. Power. Energy Syst., 2012, **36**, (1), pp.93-99

- [13] Ebrahimi, J, Babaei, E & Gharehpetian, GB 2012, 'A new multilevel converter topology with reduced number of power electronic components,' IEEE Transactions on Industrial Electronics, vol. 59, no. 2, pp. 655-667.

- [14] Ruiz-Caballero, DA, Ramos-Astudillo, RM & Mussa, SA & Heldwein, ML 2010, 'Symmetrical hybrid multilevel DC–AC converters with reduced number of insulated DC supplies,' IEEE Transaction on Industrial Electronics., vol. 57, no. 7, pp. 2307–2314.

- [15] Thamizharasan, S., Baskaran, J., Ramkumar, S., *et al.*: 'A new dual bridge multilevel DC link inverter topology', Int. J. Elect. Power. Energy Syst., 2013, **45**, (1), pp.376-383.