# DESIGN AND ANALYSIS OF AN IMPROVED HIGH GAIN NON ISOLATED INTERLEAVED BOOST CONVERTER FOR SOLAR PHOTOVOLTAIC APPLICATIONS

# S. LAKSHMI<sup>1</sup>, R. RAMAPRABHA<sup>2</sup>

PERI Institute of Technology, Tamilnadu 600048, India<sup>1</sup> SSN College of Engineering, Tamilnadu 603110, India<sup>2</sup> lklakshmikumar3@gmail.com<sup>1</sup> ramaprabhar@ssn.edu.in<sup>2</sup>

Abstract: In this paper, a novel non isolated four phase interleaved boost converter (IBC) with high voltage gain and reduced stress has been derived. This converter topology is intended to achieve a high step up gain without applying high duty cycle, utilizing input parallel and output series configuration. With less number of components, switching loss and conduction loss are also much reduced. Uniform current sharing without adding complex control methods reduces input ripple current. Due to reduced current ripple at input side and optimal number of phases, this converter is suitable for photovoltaic interface. The design equations has been derived and analyzed for the proposed converter. The theoretical analysis and simulation results validate the performance of the converter.

**Key words:** Gain, voltage stress, photovoltaic cells, pulse width modulation, voltage control.

#### 1. Introduction

Energy crisis is the major problem existing all over the world. Due to this shortage of energy, renewable energy sources like wind, ocean, solar cells and fuel cells are widely used. But the problem with renewable energy source is inherent low voltage characteristics. Hence a high quality power conditioning circuit has to be designed. Poor efficiency and high duty ratio to obtain high voltage gain are the main drawbacks of conventional boost and buck—boost converters. High duty ratio leads to large reverse recovery problem which increases the conduction loss and stress on switches which leads to high voltage spikes [1].

Many researches have been carried over to develop a converter with a high step-up voltage gain and without an extremely high duty ratio [2]. A DC–DC flyback converter is a simple isolated structure with a high step-up voltage gain, but the transformer leakage inductance produces a high voltage stress across the main switches. To reduce the stress of the switch and to reuse the leakage inductance energy, some novel energy regeneration technique has been proposed [3-4]. Converters with isolated topology,

like phase shifted full bridge converters can achieve a high step-up gain by increasing the turn's ratio of the transformer. But the problem is that the output power will be reduced with higher current ripple which mainly affects the life of the input side capacitor. Hence to reduce further effects of large input current ripple, more number of electrolytic capacitor are used. It is also detected that the output voltage is very less than the voltage stress of the diode hence the efficiency of the circuit depraves. Isolated currenttype converters such as the active clamp dual boost converters, full-bridge boost converters with active clamp [5], produces high efficiency and high gain, but the starting operation of these converters must be separately. Moreover, closed analyzed controllers, sensors and other switching devices increase the overall cost. To enhance performance of a standalone PV system whose power output keeps changing with the radiation, automatic sliding mode control technique is chosen [6]. To increase the efficiency of the system and to decrease the cost, a non isolated dc/dc converter [7] will be the best choice. The capacitor-based converters proposed in [8-10] achieves large voltage conversion ratio improving the efficiency, but high transient current and large conduction losses occurs in this switched capacitor technique.

The converter topology with high voltage gain [11–13] that utilizes leakage inductance energy for charging the capacitors with reduced stress is presented, however the input current ripple is high. The interleaved voltage doublers [14-17] with reduced stress and instinctive current sharing capability have been proposed. A high step-up ratio converter with high voltage gain without high duty cycle using switched inductor technique [18] and high gain converter for PV generation system with built in transformer voltage doubler cell using ZVT have been studied. The high step-up converter [19] with ZVT with built in transformer is proposed, however leakage inductance due transformer cause

loss. Besides, to obtain extremely high step-up conversion, many switched capacitor cells are required which increases the circuit complexity [20]. For power factor correction in front end universal line with high efficiency, there is no much voltage gain as well as the stress across switches remains high [21]. Various converter topologies with high gain and reduced stress across the switches are discussed in [22–23].

Energy efficiency of switched-capacitor converters was presented in [24] in which some design rules for high efficient converters have been presented. In [25] switching loss and electromagnetic interference with soft switching technique without using extra components have been analyzed. To reduce the switching loss and electromagnetic interference, many converter topologies have been presented based on a switched-capacitor cell concept using soft switching technique [26]. Ultra high gain converter is introduced in [27], but the diode stress is high. Each converter has its own merits and demerits.

Based on the literature survey, a high power conditioning circuit with very high voltage gain, with reduced losses, with reduced voltage stress has to be designed and analyzed. A two phase transformer-less adjustable voltage quadrupler dc-dc converter with reduced semiconductor voltage stress and high gain is proposed in [28]. This converter provides large step-up voltage conversion ratio with no higher duty ratio and no much complexity but the voltage stress of diodes still remains high.

In this paper, a new topology of four phase transformer-less adjustable voltage quadrupler topology is proposed. It integrates four inductors parallel with each other at the input side for automatic current sharing capability to achieve a high voltage gain. Besides the reduction in the voltage stress of active switches and diodes, the overall conversion efficiency is highly enhanced. Section 2 outlines the circuit topology and the operating principle for each mode of operation. The steady state analysis is further analyzed in Section 3 that provides detailed converter characteristics. The functioning of the proposed system has been validated through MatLab/Simulink the simulation results that provide detailed information about the stress, efficiency and gain for the converter is presented in Section 4 for demonstrating the merits of the proposed converter. Finally, conclusions are offered in the last section.

# 2. Modes of operation of the proposed converter

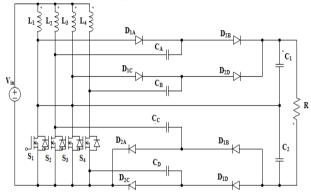

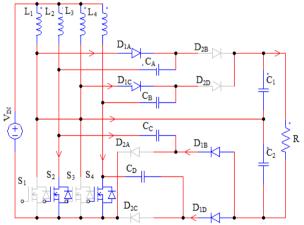

The designed converter topology is derived from a two-phase voltage quadrupler. Fig. 1 shows the novel four phase quadrupler topology. It can be seen that two blocking (auxiliary) capacitors and four diodes are added in the existing topology for a four phase so that during the energy transfer period, the stored energy in the inductor is stored in one capacitor and partial inductor stored energy together with energy stored in the other capacitor is transferred to the output to achieve higher voltage gain. The proposed voltage gain is multiple times higher than that of the interleaved two-phase boost converter. The voltage spike existing across active switches and diodes are much lower than that of the existing converter topologies. The proposed converter produces involuntary uniform current sharing capability without additional circuit and complex control methods. The detailed operating principle can be illustrated as follows.

Fig.1. Configuration of four phase proposed converter

The main objective of this paper is to reduce the stress across the switches with high voltage gain in continuous conduction mode (CCM) and that can only be achieved when the duty cycle is greater than 50% hence, the steady-state analysis is made only for CCM mode. But, with duty cycle lower than 50% that is in Discontinuous Conduction Mode (DCM), as there is no enough energy transfer from the energy storage inductors to the auxiliary capacitors, it is not possible to get the high voltage gain for duty ratio greater than 50%.

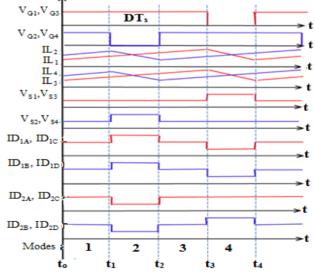

Fig.2. Key operating waveforms of the proposed converter at CCM

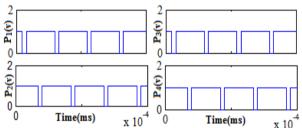

Due to the charge balance of the blocking capacitor, automatic current sharing characteristic is possible. With duty cycle is less than 50%, the converter does not produce the automatic current sharing capability. Hence the current-sharing control between each phase should be taken into account. Basically, the working principle of the converter is classified into four modes of operation. The gating signals with 180° phase shift and some key operating waveforms are shown in Fig. 2

In order to simplify the circuit analysis of the proposed converter, it is assumed as

- All components are ideal components

- The voltages across capacitors can be considered as constant approximately.

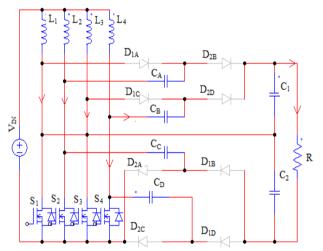

**2.1 Mode 1** [ $t_0 \le t \le t_1$ ]: In mode 1, switches  $S_1$ ,  $S_2$ ,  $S_3$ and  $S_4$  (Fig. 3) are turned ON and all the diodes  $D_{IA}$ ,  $D_{1B}$ ,  $D_{2A}$ ,  $D_{2B}$ ,  $D_{1C}$ ,  $D_{1D}$ ,  $D_{2C}$ , and  $D_{2D}$  are OFF. It is seen that the inductor currents  $i_{L1}$ ,  $i_{L2}$ ,  $i_{L3}$  and  $i_{L4}$  are increasing to store energy in  $L_1$ ,  $L_2$ ,  $L_3$  and  $L_4$ , respectively. The voltages across diodes  $D_{IA}$ ,  $D_{2A}$ ,  $D_{1C}$ , and  $D_{2C}$  are clamped to capacitor voltage  $V_{CA}$ ,  $V_{CB}$ ,  $V_{CC}$  and  $V_{CD}$ , respectively. The voltages across the diodes  $D_{IB}$  and  $D_{2B}$  are clamped to  $V_{C2}$  minus  $V_{CB}$  and  $V_{CI}$  minus  $V_{CA}$ . The voltages across the diodes  $D_{1D}$  and  $D_{2B}$  are clamped to  $V_{C4}$  minus  $V_{CD}$  and  $V_{C3}$  minus  $V_{CC}$  respectively. The load power is supplied from capacitors  $C_1$ , and  $C_2$ .

Fig.3. Equivalent circuit for Mode 1 Operation

The corresponding state equations are given as follows

$$L_1 \frac{di_{L1}}{dt} = V_{in} \tag{1}$$

$$L_2 \frac{di_{L2}}{dt} = V_{in} \tag{2}$$

$$L_3 \frac{di_{L3}}{dt} = V_{in} \tag{3}$$

$$L_4 \frac{di_{L4}}{dt} = V_{in} \tag{4}$$

During this mode of operation the current flowing

During this mode of operation the current flowing through the auxiliary capacitors  $C_A$ ,  $C_B$ ,  $C_C$  and  $C_D$  is equal to zero.

$$C_A \frac{dv_{CA}}{dt} = 0 (5)$$

$$C_B \frac{dv_{CB}}{dt} = 0 (6)$$

$$C_{C} \frac{dv_{CC}}{dt} = 0$$

$$C_{D} \frac{dv_{CD}}{dt} = 0$$

(8)

$$C_D \frac{dv_{CD}}{dt} = 0 (8)$$

The current flowing through the output capacitors  $C_1$ , and  $C_2$  is given by

$$C_1 \frac{dv_{C1}}{dt} = -\frac{\left(v_{C1} + v_{C2}\right)}{R}$$

$$C_2 \frac{dv_{C2}}{dt} = -\frac{\left(v_{C1} + v_{C2}\right)}{R}$$

$$(9)$$

$$C_2 \frac{dv_{C2}}{dt} = -\frac{\left(v_{C1} + v_{C2}\right)}{R} \tag{10}$$

**2.2** *Mode* 2  $[t_1 \le t \le t_2]$ : In this operation mode, switch  $S_1$  and  $S_3$  conducts, whereas  $S_2$  and  $S_4$  are turned OFF. Diodes  $D_{2A}$ ,  $D_{2B}$ ,  $D_{2C}$  and  $D_{2D}$  conduct.

Part of stored energy in inductor  $L_2$ ,  $L_4$  and stored energy of  $C_A$ ,  $C_C$  is now released to output capacitor  $C_1$ ,  $C_3$  and load and meanwhile, part of stored energy in inductor  $L_2$  and  $L_4$  is stored in  $C_B$  and  $C_D$ respectively. The corresponding equivalent circuit is shown in Fig.4.

Fig.4. Equivalent circuit for Mode 2 Operation

In this mode of operation, capacitor voltage  $V_{C1}$  is equal to  $V_{CB}$  plus  $V_{CA}$  and similarly capacitor voltage  $V_{C2}$  is equal to  $V_{CD}$  plus  $V_{CC}$ . Thus,  $i_{L1}$ ,  $i_{L3}$  still increases continuously and  $i_{L2}$ ,  $i_{L4}$  decreases linearly.

The corresponding state equations are given as follows:

$$L_1 \frac{di_{L1}}{dt} = V_{in} \tag{11}$$

$$L_2 \frac{di_{L2}}{dt} = V_{in} + v_{CA} - v_{C1} = V_{in} - v_{CB}$$

(12)

$$L_3 \frac{di_{L3}}{dt} = V_{in} \tag{13}$$

$$L_4 \frac{di_{L4}}{dt} = V_{in} + v_{CC} - v_{C1} = V_{in} - v_{CD}$$

(14)

$$C_A \frac{dv_{CA}}{dt} = i_{CB} - i_{L2} \tag{15}$$

$$C_B \frac{dv_{CB}}{dt} = i_{CA} + i_{L2} \tag{16}$$

$$C_C \frac{dv_{CC}}{dt} = i_{CD} - i_{L4} \tag{17}$$

$$C_D \frac{dv_{CD}}{dt} = i_{CC} + i_{L4} \tag{18}$$

$$C_{1} \frac{dv_{C1}}{dt} = -i_{CA} - \frac{(v_{C1} + v_{C2})}{R}$$

(19)

$$C_1 \frac{d}{dt} = -l_{CA} - \frac{d}{R}$$

$$C_2 \frac{dv_{C1}}{dt} = -\frac{(v_{C1} + v_{C2})}{R}$$

(20)

- **2.3 Mode 3**  $[t_2 \le t \le t_3]$ : In this operating mode, all the switches  $S_1$ ,  $S_2$ ,  $S_3$  and  $S_4$  are turned ON and that is shown in Fig.3. The corresponding equivalent circuit turns out to be the same as Fig. 3.

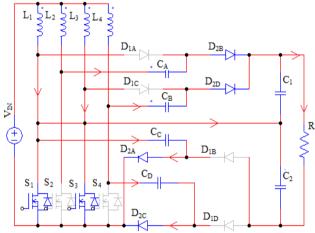

- **2.4 Mode 4**  $[t_3 \le t \le t_4]$ : For this operation mode, switches  $S_2$  and  $S_4$  remains conducting and  $S_1$  and  $S_3$ is turned OFF. Diodes  $D_{1A}$ ,  $D_{1B}$ ,  $D_{1C}$  and  $D_{1D}$  become conducting. The corresponding equivalent circuit is shown in Fig. 5.

Fig.5. Equivalent circuit for Mode 4 Operation

It is seen from Fig. 5 that the part of stored energy in inductor  $L_1$  and  $L_3$  as well as the stored energy of  $C_B$  and  $C_D$  is now released to output capacitor  $C_2$  and load. Meanwhile, part of stored energy in inductor  $L_1$  and  $L_3$  is stored in  $C_A$  and  $C_C$ . In this mode, the output capacitor voltage  $V_{C2}$  is equal to sum of voltages across all the blocking capacitors.

Thus,  $i_{L1}$  and  $i_{L3}$  decrease linearly and  $i_{L2}$  and  $i_{L4}$ still increases continuously. It can be seen from the waveforms, the voltage stresses on the diodes are much reduced and uniform current sharing is achieved.

The corresponding state equations are given as

$$L_{1}\frac{di_{L1}}{dt} = V_{in} - v_{C2} + v_{CB} = V_{in} - v_{CA}$$

(21)

$$L_2 \frac{di_{L2}}{dt} = V_{in} \tag{22}$$

$$L_{3} \frac{di_{L3}}{dt} = V_{in} - v_{C2} + v_{CD} = V_{in} - v_{CC}$$

(23)

$$L_4 \frac{di_{L4}}{dt} = V_{in} \tag{24}$$

$$C_A \frac{dv_{CA}}{dt} = i_{CB} + i_{L1} \tag{25}$$

$$C_B \frac{dv_{CB}}{dt} = i_{CA} - i_{L1} \tag{26}$$

$$C_C \frac{dv_{CC}}{dt} = i_{CD} + i_{L2} \tag{27}$$

$$C_D \frac{dv_{CD}}{dt} = i_{CC} - i_{L2} \tag{28}$$

$$C_{1} \frac{dv_{C1}}{dt} = -\frac{\left(v_{C1} + v_{C2}\right)}{R}$$

$$C_{2} \frac{dv_{C2}}{dt} = -\frac{\left(v_{C1} + v_{C2}\right)}{R}$$

(29)

$$C_2 \frac{dv_{C2}}{dt} = -\frac{\left(v_{C1} + v_{C2}\right)}{R} \tag{30}$$

From the above equations and illustrations, it can be found that the operation of a four phase interleaved boost converter is simple with excellent features which can be best suited for PV source as The performance analysis of the proposed converter is assumed to be in CCM for simplified analysis.

# 3. Design Considerations

The design procedure of the proposed topology based on the following specifications is described as follows.

Input Voltage = 32 V

Output Voltage = 1024 V

Output Power = 1638 W

Switching Frequency = 40 kHz

# 3.1. Input Inductance

$$L_{in} = \frac{V_{in}(1-D)D}{\Delta I_I f_S} \tag{31}$$

D represents the duty ratio of the switches.

$\Delta I_I$  represents the peak to peak ripple current of the Inductor.

$f_s$  represents the switching frequency.

$\Delta I_I$  is chosen in the range between 20 to 40 % of the output Current Io.

# 3.2. Auxiliary Capacitance

$$C_A = \frac{I_o D}{\Delta V_{CA} f_s} \tag{32}$$

$\Delta V_{CA}$  represents the peak to peak ripple voltage of the blocking capacitor. It is approximately chosen

# 3.3. Output Capacitor

$$C_O = \frac{V_O D}{\Delta V_{CO} f_S R} \tag{33}$$

$\Delta V_{CO}$  represents the peak to peak ripple voltage of the output capacitor.

It is chosen to be 4 to 5 % of  $\Delta VC_{\Delta}$ .

R represents the load resistance.

## 3.4. Voltage Gain

$$\frac{V_o}{V_{in}} = \frac{8}{1 - D} \tag{34}$$

# 3.5. Power Output

$$P_O = \frac{V_O^2}{R} \tag{35}$$

# 3.6. Output Current

$$I_O = \frac{P_O}{V_O} \tag{36}$$

## 4. Analysis of the proposed Converter

# 4.1 Voltage Gain

From Fig.3 and Fig.5 the volt-time relationship of the inductor  $L_1$ ,  $L_2$ ,  $L_3$  and  $L_4$  can be obtained as follows:

$$2V_{in}D + V_{in}(1-D) + (V_{in} - V_{CA})(1-D) = 0$$

(37)

$$2V_{in}D + V_{in}(1-D) + (V_{in} - V_{CB})(1-D) = 0$$

(38)

$$2V_{in}D + V_{in}(1-D) + (V_{in} - V_{CC})(1-D) = 0$$

$$2V_{in}D + V_{in}(1-D) + (V_{in} - V_{CD})(1-D) = 0$$

(39)

$$(40)$$

(40)

Voltage  $V_{C1}$  and  $V_{C2}$  can be derived as follows by substituting  $V_{CA}$  and  $V_{CB}$  in equations (37), (38), (39)

$$V_{C1} = V_{CA} + V_{CC} = \frac{4}{1 - D} V_{in} \tag{41}$$

$$V_{C2} = V_{CB} + V_{CD} = \frac{4}{1 - D} V_{in}$$

(42)

The output voltage will be equal to the sum of the voltage across the output capacitors  $C_1$  and  $C_2$ .

$$V_O = V_{C1} + V_{C2} = \frac{8}{1 - D} V_{in} \tag{43}$$

The voltage conversion ratio M of this converter

can be obtained as follows:

$$M = \frac{V_o}{V_{in}} = \frac{8}{1 - D} \tag{44}$$

## 4.2 Voltage stress on Semiconductor Components

The voltage ripples on the capacitors can be ignored to simplify the voltage stress on the switches and diodes of the proposed converter. The voltage stresses on active power switches  $S_1$ ,  $S_2$ ,  $S_3$  and  $S_4$  can be obtained directly as shown in the following equation:

The voltage stress on the active power switches can be expressed as

$$V_{S1ma_X} = V_{S2max} = V_{S3max} = V_{S4max} = \frac{V_{in}}{1-D}$$

(45)

$$V_{S1ma_x} = V_{S2\max} = V_{S3\max} = V_{S4\max} = \frac{V_o}{8}$$

(46)

From (46), it can be seen that the voltage stress of the active switches of the proposed converter is equal to one eighth of the output voltage. As a result, lower voltage rating devices are used which enables to further reduce both switching and conduction losses.

The open circuit voltage stress of diodes  $D_{1A}$ ,  $D_{2A}$ ,  $D_{1B}$ ,  $D_{2B}$ ,  $D_{1C}$ ,  $D_{2C}$ ,  $D_{1D}$ , and  $D_{2D}$  can be obtained directly as shown in equation (47) and (48)

$$V_{D1A\,\text{max}} = V_{D1B\,\text{max}} = V_{D1C\,\text{max}} = V_{D1D\,\text{max}} = \frac{V_O}{2}$$

(47)

$$V_{D2B\max} = V_{D2D\max} = \frac{V_o}{2}$$

$$V_{D2A\max} = V_{D2C\max} = \frac{V_o}{4}$$

(48)

From (47) and (48) it is clear that the maximum resulting voltage stress of diodes is equal to  $V_0/2$ . Hence, the proposed converter enables one to adopt lower voltage rating diodes to further reduce conduction losses.

# 4.3 Characteristic of Uniform Input Inductor Current Sharing

State space averaging technique is utilized to get the averaged state equations as follows:

$$L_{1} \frac{di_{L1}}{dt} = V_{in} - (1 - D)V_{CA}$$

(49)

$$L_2 \frac{di_{L2}}{dt} = V_{in} - (1 - D)V_{CB}$$

(50)

$$L_3 \frac{di_{L3}}{dt} = V_{in} - (1 - D)V_{CC}$$

(51)

$$L_4 \frac{di_{L4}}{dt} = V_{in} - (1 - D)V_{CD}$$

(52)

State space equations of auxiliary capacitors can be expressed as follows:

$$C_{A} \frac{dvC_{A}}{dt} = \frac{(1-D)\left[RC_{A}C_{3} - C_{P}C_{Q}(V_{C1} + V_{C2})\right]}{RC_{P}}$$

(53)

$$C_{B} \frac{dvC_{B}}{dt} = \frac{(1-D)\left[RC_{B}C_{4} - C_{P}C_{Q}(V_{C1} + V_{C2})\right]}{RC_{R}}$$

(54)

$$C_{C} \frac{dvC_{C}}{dt} = \frac{(1 - D) \left[ RC_{C}C_{5} - C_{P}C_{Q} \left( V_{C1} + V_{C2} \right) \right]}{RC_{R}}$$

(55)

$$C_D \frac{dvC_D}{dt} = \frac{(1 - D) \left[ RC_D C_6 - C_P C_Q \left( V_{C1} + V_{C2} \right) \right]}{RC_R}$$

(56)

Where

$$\begin{pmatrix} C_{eq1}I_{L1}(C_2 + C_B) - C_{eq2}I_{L2}C_1 \\ + C_{eq3}I_{L3}(C_2 + C_D) - C_{eq4}I_{L4}C_1 \end{pmatrix} = C_3$$

(57)

$$\begin{pmatrix} C_{eq2}I_{L2}(C_1 + C_A) - C_{eq1}I_{L1}C_2 \\ + C_{eq4}I_{L4}(C_1 + C_C) - C_{eq3}I_{L3}C_2 \end{pmatrix} = C_4$$

(58)

$$\begin{pmatrix} C_{eq3}I_{L3}(C_2 + C_D) - C_{eq4}I_{L4}C_1 \\ + C_{eq1}I_{L1}(C_1 + C_B) - C_{eq2}I_{L4}C_1 \end{pmatrix} = C_5$$

(59)

$$\begin{pmatrix} C_{eq4}I_{L4}(C_1 + C_C) - C_{eq3}I_{L3}C_2 \\ + C_{eq2}I_{L2}(C_1 + C_A) - C_{eq1}I_{L1}C_2 \end{pmatrix} = C_6$$

(60)

$$\dot{C}_A C_B C_C C_D = C_P \tag{61}$$

$$C_{eq1} + C_{eq2} + C_{eq3} + C_{eq4} = C_Q$$

(62)

$$C_{eq1}C_{eq2}C_{eq3}C_{eq4} = C_R (63)$$

$$C_{1} \frac{dv_{C1}}{dt} = \frac{(1-D)C_{1}(C_{A}I_{L2}R + C_{C}I_{L4}R)}{C_{C1}+V_{C2}}$$

$$-\frac{D(V_{C1}+V_{C2})}{C_{eq1}C_{eq3}R}$$

(64)

$$-\frac{D(V_{C1} + V_{C2})}{R}$$

$$(1 - D)C_2(C_B I_{L1} R + C_D I_{L3} R)$$

$$C_2 \frac{dv_{C2}}{dt} = \frac{-C_T(V_{C1} + V_{C2})}{C_{eq2} C_{eq4} R}$$

$$-\frac{D(V_{C1} + V_{C2})}{D}$$

(65)

Where

$$C_T = C_A + C_B + C_C + C_D$$

$C_{eq1} = C_1 C_A + C_1 C_B + C_A C_B$

$C_{eq2} = C_2 C_A + C_2 C_B + C_A C_B$

$C_{eq3} = C_1 C_C + C_1 C_D + C_C C_D$

$C_{eq4} = C_2 C_C + C_2 C_D + C_C C_D$

Where  $i_{L1}$ ,  $i_{L2}$ ,  $i_{L3}$ ,  $i_{L4}$ ,  $v_{CA}$ ,  $v_{CB}$ ,  $v_{CC}$ ,  $v_{CD}$ ,  $v_{C1}$ ,  $v_{C2}$  denotes average state space values.  $I_{L1}$ ,  $I_{L2}$ ,  $I_{L3}$ ,  $I_{L4}$ ,  $V_{CA}$ ,  $V_{CB}$ ,  $V_{CC}$ ,  $V_{CD}$ ,  $V_{C1}$  and  $V_{C2}$  denote corresponding

DC values.

$$I_{o} = \frac{\left(V_{C1} + V_{C2}\right)}{R} \tag{66}$$

By selecting  $C_1 = C_2 = C_X$ ,  $C_A = C_B = C_C = C_D = C_Y$ , one can get the corresponding dc solutions as follows:

$$I_{L1} = I_{L2} = I_{L3} = I_{L4} = \left(\frac{4}{1-D} + \frac{DC_Y}{(1-D)C_X}\right)I_O$$

(67)

## 4.4 Performance Comparison

The proposed converter is compared with some recent high step-up as shown in Table I. Table I summarizes the voltage gain and steady state characteristics of four different converter topologies. From Table 1, it is clear that the proposed converter achieves higher voltage gain and reduced semiconductor stress than conventional topologies of high gain converters.

Table 1 Comparison of the steady state characteristics of four different converter topologies

| Gain/<br>Stress                | Voltage<br>doubler<br>[17] | High step<br>up<br>converter<br>[18] | Ultra high<br>step up<br>converter<br>[27] | Proposed<br>Converter |

|--------------------------------|----------------------------|--------------------------------------|--------------------------------------------|-----------------------|

| Voltage<br>Gain                | $\frac{2}{(1-D)}$          | $\frac{(3-D)}{(1-D)}$                | $\frac{(3+D)}{(1-D)}$                      | $\frac{8}{1-D}$       |

| Voltage<br>stress on<br>switch | $\frac{1}{2}$              | $\frac{1}{3-D}$                      | $\frac{2}{3-D}$                            | $\frac{1}{8}$         |

| Voltage<br>Stress<br>on diode  | 1                          | $\frac{2}{(3-D)}$                    | $\frac{2}{(3+D)}$                          | $\frac{1}{2}$         |

| Number<br>of MOS-<br>FET       | 2                          | 2                                    | 1                                          | 4                     |

| Number<br>of<br>Inductor       | 2                          | 2                                    | 2                                          | 4                     |

| Number of Diode                | 2                          | 3                                    | 5                                          | 8                     |

| Number<br>of<br>capacitor      | 2                          | 3                                    | 4                                          | 6                     |

Therefore, the proposed converter is rather suitable for use in applications requiring high step-up voltage gain. The proposed converter achieves reduced voltage stress for the active switches and the diodes. As a result high efficiency can be achieved with proper design, and reduced switch components.

# 5. Simulation results

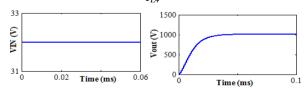

The proposed converter is analyzed for a power rating of 1700 W with an input voltage of 32 V and 1024 V output, as shown in Fig. 1. The switching frequency is chosen to be 40 kHz. The duty ratios of  $S_1$ ,  $S_2$ ,  $S_3$  and  $S_4$  equal to 0.75 and the corresponding component parameters can be obtained in Table 2.

Due to the low switch voltage stress of the proposed converter, four power MOSFETs rating of 150 V and conductive resistance of  $0.1\Omega$ , is used. Similarly, eight diodes with low forward voltage drop of 0.8 volts are chosen. The interleaved structure can effectively increase the switching frequency with reduced ripples in the input and output and so is the size of the energy storage inductors.

Table 2: Component parameters of the proposed converter

| Components                                                                         | Specification |

|------------------------------------------------------------------------------------|---------------|

| Boost Inductors L <sub>1</sub> , L <sub>2</sub> , L <sub>3</sub> , L <sub>4</sub>  | 323.9 µH      |

| Blocking Capacitors C <sub>A</sub> ,C <sub>B</sub> ,C <sub>C</sub> ,C <sub>D</sub> | 31.19 µH      |

| Output Capacitor C <sub>1</sub> ,C <sub>2</sub>                                    | 769.2 μΗ      |

The measured input voltage is 32 V, and the output voltage is 1024 V. The pulse patterns of the switches  $S_1$ ,  $S_2$ ,  $S_3$  and  $S_4$  are shown in Fig. 6. It can be observed that  $S_1$  and  $S_3$  are fired at same time whereas  $S_2$  and  $S_4$  are triggered at 180 ° phase shift. Fig.6 shows the switching pulses to all the four switches. The gating signals are given with 180° phase shift.

Fig. 6. Pulse pattern to the Switches  $S_1$ ,  $S_2$ ,  $S_3$  and  $S_4$

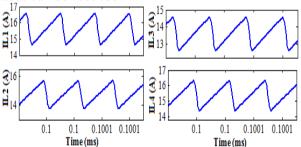

Fig. 7 shows the four-phase inductor current waveforms of the simulation results. Since input current  $I_{in}$  is equal to the sum of  $I_{L1}$ ,  $I_{L2}$ ,  $I_{L3}$ ,  $I_{L4}$  it is obvious that with the four-phase interleaving control, both input current ripples and switch conduction losses can be reduced.

Fig.7. Waveforms of inductors current  $I_{LI}$ ,  $I_{L2}$ ,  $I_{L3}$  and  $I_{L4}$

Fig.8. Waveforms of Input and Output Voltages

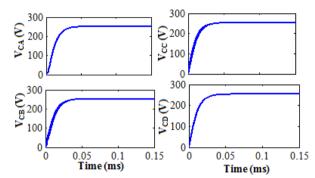

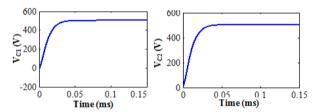

Fig. 8 shows the input and output voltage waveforms of the proposed converter. To check the validity of the capacitor voltage stress, waveforms of output capacitors and blocking capacitors are recorded as shown in Fig. 9 and 10.

Fig.9. Waveforms of the voltage across the blocking capacitors (a)  $C_A$  (b)  $C_B$  (c)  $C_C$  (d)  $C_D$

From Figure 9 and 10, it can be seen that, with the proposed converter, the voltage stresses of the output capacitors and blocking capacitors are indeed equal to one half and one fourth of the output voltage, respectively.

Fig.10. Waveforms of the voltage across the output capacitors

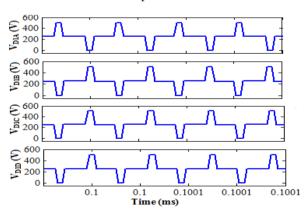

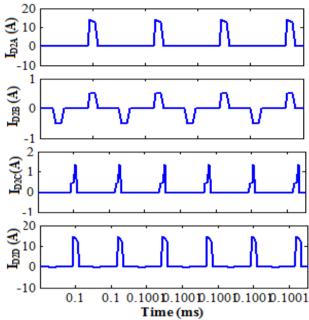

Fig.11. Waveforms of the voltage stress of  $V_{DIA}$ ,  $V_{DIB}$ ,  $V_{DIC}$  and  $V_{DID}$

Also, to check the voltage stress of blocking capacitors, one can see when the proposed converter is operated in modes 2 and 4, the voltages of capacitors  $C_A$  and  $C_B$  are clamped at  $Vin\ (I-D)$ , and when the proposed converter is operated in modes 1 and 3, all diodes are OFF, and capacitors  $C_A$ ,  $C_B$ ,  $C_C$  and  $C_D$  are isolated as open circuits; hence, the

voltages of capacitors  $C_A$ ,  $C_B$ ,  $C_C$  and  $C_D$  are kept constant. Also, the output loading is mainly supplied by capacitors  $C_1$  and  $C_2$ .

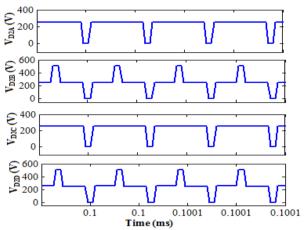

Fig.12. Waveforms of the voltage stress of  $V_{D2A}$ ,  $V_{D2B}$ ,  $V_{D2C}$  and  $V_{D2D}$

The diode voltage waveforms of the simulation results are shown in Fig. 11 and 12, which indicates that the maximum voltage cross diodes  $V_{DIA}$ ,  $V_{DIB}$ ,  $V_{DIC}$ ,  $V_{DID}$ ,  $V_{D2D}$  and  $V_{D2B}$  equals 200 V which is indeed equal to one-half of the output voltage. The maximum voltage crosses diode  $V_{D2A}$  and  $V_{D2C}$  is 100 V which is equal to one fourth of the output voltage as expected. Therefore, the voltages across  $C_A$ ,  $C_B$ ,  $C_C$  and  $C_D$  can be maintained at constant values though  $C_A$ ,  $C_B$ ,  $C_C$  and  $C_D$  are with rather small capacitance.

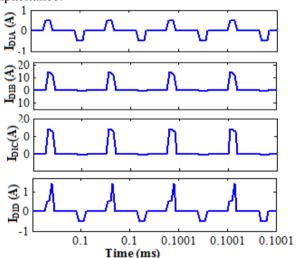

Fig.13. Waveforms of the current flowing through of  $I_{DIA}$ ,  $I_{DIB}$ ,  $I_{DIC}$  and  $I_{DID}$

The diode current waveforms of the simulation results are shown in Fig. 13 and 14. In the proposed topology, low-voltage-rating rectifier diodes are used to reduce the conduction loss. Due to the help of the blocking capacitor, the output current ripples are reduced. By analyzing the power losses distribution, it can be concluded that the major losses come from

the active switches, the diodes, and the input inductors

Fig.14. Waveforms of the current flowing through of  $I_{D2A}$ ,  $I_{D2B}$ ,  $I_{D2C}$  and  $I_{D2D}$

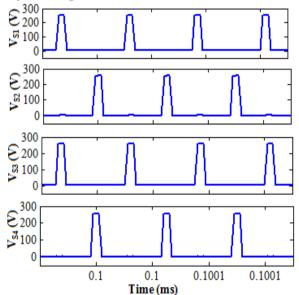

From Fig. 15, it is observed that the voltage stress of the active switches is equal to one fourth of the output voltage

Fig.15. Waveforms of the voltage stress of switches  $V_{SI}$ ,  $V_{S2}$ ,  $V_{S3}$  and  $V_{S4}$

# 6. Conclusion

In this paper, a four phase transformer-less adjustable voltage quadrupler DC–DC converter with high voltage transfer gain without adopting an extreme large duty cycle and reduced semiconductor voltage stress is proposed. The proposed topology

utilizes input-parallel output-series configuration. The proposed converter not only reduces the voltage stress of the switches and diodes but also achieves high step-up voltage gain. Both switching and conduction losses are reduced by choosing lower voltage rating MOSFETs and diodes. In addition, there is an automatic uniform current sharing characteristic due to the charge balance of the blocking capacitor, without adding any additional complex circuits. The operation principle with detailed steady analysis is presented. With many good features such as high gain, reduced voltage stress, reduced ripples and high efficiency, it can be concluded that the proposed converter is highly suitable for high step-up voltage gain applications. The results of simulations run by Matlab software validate the performance of the converter. The proposed system with advanced control algorithm can be used for interfacing with PV applications.

### Acknowledgement

The authors wish to thank the management of PERI Institute of Technology and SSN College of Engineering, Chennai for providing all the computational facilities to carry out this work.

## References

- [1] Qun Zhao, Fengfeng Tao, Fred C. Lee, Peng Xu, Jia Wei.: A simple and effective to alleviate the Rectifier Reverse-Recovery Problem in Continuous-Current-Mode Boost Converter. In IEEE Transactions on Power Electronics Vol. 16, no. 5, pp. 649–658, 2001

- [2] Qun Zhao and Fred C. Lee.: *High-efficiency*, *High Step-Up DC–DC Converters*. IEEE Transactions on Power Electronics, Vol. 18, no. 1, pp. 65–73, 2003.

- [3] Bor Ren Lin, Fang-Yu Hsieh.: Soft-Switching Zeta–Fly Back Converter with a Buck–Boost type of Active Clamp. In IEEE Transactions on Industrial Electronics, Vol. 54, no. 5, pp. 2813–2822, 2007.

- [4] Chien Ming Wang.: A Novel ZCS-PWM Fly Back Converter with a simple ZCS PWM Commutation Cell. In IEEE Transactions on Industrial Electronics Vol. 55, no. 2, pp. 749–757, 2008.

- [5] Jung Min Kwon, Bong-Hwan Kwon.: High Step-Up Active-Clamp Converter with Input-Current Doubler and Output-Voltage Doubler for Fuel Cell Power Systems. In IEEE Transactions on Power Electronics, Vol. 24, no. 1, pp. 108–115, 2009.

- [6] Rong Jong Wai, Wen-Hung Wang.: *Grid-Connected Photovoltaic Generation System*. In IEEE Transactions on Circuits and Systems I, Regular Papers, Vol. 55, no. 3, pp. 953–964, 2008.

- [7] Marcos Prudente, Luciano L. Pfitscher, Gustavo Emmendoerfer, Eduardo F. Romaneli, Roger Gules.: *Voltage Multiplier Cells Applied to Non-Isolated DC–DC Converters*. In IEEE Transactions on Power Electronics, Vol. 23, no. 2, pp. 871–887, 2008.

- [8] Fan Zhang, Lei Du, Fang Zheng Peng, Zhaoming Qian.: A New Design Method For High Power High-Efficiency Switched-Capacitor DC-DC Converters. In IEEE Transactions on Power Electronics, Vol. 23, no. 2, pp. 832–840, 2008.

- [9] Esam H. Ismail, Mustafa A. Al-Saffar, Ahmad J. Sabzali, Abbas A. Fardoun.: A Family of Single-Switch PWM Converters with High Step-Up Conversion Ratio. In IEEE Transactions on Circuits Systems I, Regular Papers, Vol. 55, no. 4, pp. 1159–1171, 2008.

- [10] Boris Axelrod, Yefim Berkovich, Adrian Ioinovici.: Switched-Capacitor/ Switched-Inductor Structures for getting Transformer Less Hybrid DC-DC PWM Converters. In IEEE Transactions on Circuits Systems I, Regular Papers, Vol. 55, no. 2, pp. 687–696, 2008.

- [11] Lung-Sheng Yang, Tsorng-Juu Liang, Hau-Cheng Lee, Jiann-Fuh Chen.: Novel High Step-Up DC-DC Converter with Coupled-Inductor and Voltage-Doublers Circuits. In IEEE Transactions on Industrial Electronics, Vol. 58, no. 9, pp. 4196–4206, 2011.

- [12] Shih-Kuen Changchien, Tsorng-Juu Liang, Jiann-Fuh Chen, Lung-Sheng Yang.: *Novel High Step-Up DC–DC Converter for Fuel Cell Energy Conversion System.* In IEEE Transactions on Industrial Electronics, Vol. 57, no. 6, pp. 2007–2017, 2010.

- [13] Wuhua Li, Xiangning He.: A Family of Interleaved DC/DC Converters deduced from a Basic Cell with Winding-Cross-Coupled Inductors (WCCIs) for High Step-Up or Step-Down Conversions. In IEEE Transactions on Power Electronics, Vol. 22, no. 4, pp. 1499–1507, 2008.

- [14] Wuhua Li, Yi Zhao, Jiande Wu, Xiangning He.: Interleaved High Step-Up Converter with Winding-Cross-Coupled Inductors and Voltage Multiplier Cells. In IEEE Transactions on Power Electronics, Vol. 27, no. 1, pp. 133–143, 2012.

- [15] Gustavo A. L. Henn, R. N. A. L. Silva, Paulo P. Prac¸a, Luiz H. S. C. Barreto, Demercil S. Oliveira.: Interleaved-Boost Converter with High Voltage Gain. In IEEE Transactions on Power Electronics, Vol. 25, no. 11, pp. 2753–2761, 2010.

- [16] Wuhua Li, Yi Zhao, Yan Deng, Xiangning He.: Interleaved Converter with Voltage Multiplier Cell for High Step-Up and High Efficiency Conversion. In IEEE Transactions on Power Electronics, Vol. 25, no. 9, pp. 2397–2408, 2010.

- [17] Yungtaek Jang , Milan M. Jovanovic.: Interleaved Boost Converter with Intrinsic Voltage-Doubler Characteristic for Universal-Line PFC Front End. In IEEE Transactions on Power Electronics, Vol. 22, no. 4, pp. 1394–1401, 2007.

- [18] Lung-Sheng Yang, Tsorng-Juu Liang, Jiann-Fuh Chen.: Transformer Less DC-DC Converters with High Step-Up Voltage Gain. In IEEE Transactions on Industrial Electronics, Vol. 56, no. 8, pp. 3144– 3152, 2009.

- [19] Weichen Li, Xin Xiang, Chushan Li, Wuhua Li, Xiangning He.: Interleaved High Step-Up ZVT Converter with Built-In Transformer Voltage Doubler Cell for Distributed PV Generation System. In IEEE Transactions on Industrial Electronics, Vol. 28, no. 1, pp. 300–313, 2013.

- [20] Sanghyuk Lee, Pyosoo Kim, Sewan Choi.: *High Step-Up Soft-Switched Converters using Voltage Multiplier Cells*. In IEEE Transactions on Power Electronics, Vol. 28, no. 7, pp. 3379–3387, 2013.

- [21] Kuo-Ching Tseng, Chi-Chih Huang, Wei-Yuan Shih.: A High Step-Up Converter with a Voltage Multiplier Module for a Photovoltaic System. In IEEE Transactions Power Electronics, Vol. 28, no. 6, pp. 3047–3057, 2013.

- [22] Shih-Ming Chen, Tsorng-Juu Liang, Lung-Sheng Yang, Jiann-Fuh Chen.: A Boost Converter with Capacitor Multiplier and Coupled Inductor for AC Module Applications. In IEEE Transactions Industrial Electronics, Vol. 60, no. 4, pp. 1503–1511, 2013.

- [23] Ching-Ming Lai, Ching-Tsai Pan, Ming-Chieh Cheng.: High-Efficiency Modular High Step-Up Interleaved Boost Converter for DC-Micro Grid Applications. In IEEE Transactions Industrial. Electronics, Vol. 48, no. 1, pp. 161–171, 2012.

- [24] Chun-Kit Cheung, Siew-Chong Tan, Chi K. Tse, Adrian Ioinovici.: *On Energy Efficiency of Switched-Capacitor Converters*. In IEEE Transactions Power Electronics, Vol. 28, no. 2, pp. 862–876, 2013.

- [25] Ke Zou, Mark J. Scott, Jin Wang.: Switched-Capacitor-Cell-Based Voltage Multipliers and DC–AC Inverters. In IEEE Transactions on Industrial Applications, Vol. 48, no. 5, pp. 1598–1609, 2012.

- [26] Luiz Henrique S. C. Barreto, Paulo Peixoto Prac¸a, Demercil S. Oliveira, Ranoyca N. A. L. Silva.: High-Voltage Gain Boost Converter based on Three-State Commutation Cell for Battery Charging using PV Panels in a Single Conversion Stage. In IEEE Transactions on Power Electronics, Vol. 29, no. 1, pp. 150–158, 2014.

- [27] Abbas A. Fardoun; Esam H. Ismail,: *Ultra step-up DC–DC converters with reduced switch stress*. In IEEE Transactions on Industrial Applications, vol. 46, no. 5, pp. 2025–2034, Oct. 2010.

- [28] Ching-Tsai Pan, Chen-Feng Chuang, Chia-Chi Chu.: A Novel Transformer-less Adaptable Voltage Quadrupler DC Converter with Low Switch Voltage Stress. In IEEE Transactions on Power Electronics, Vol. 29, no. 9, 2014.