# A Self Balancing Space Vector PWM for Z Source T Multilevel Inverter

# C.Santhakumar\*, R.Shiva kumar\*\*, C.Bharatiraja\*\*\*,

\* Assistant Professor Department of Electrical and Electronics Engineering.K.S. R I.E.T, India.

\*\*Professor Department of Electrical and Electronics Engineering, Sona College of Technology, India.

\*\*\*Department of Electrical and Electronics Engineering, SRM Institute of Science and Technology, Chennai.

Abstract— This paper presents a Z Source -T shape - Neurtal point Diode Clamped (NPC) - Multi Level Inverter (MLI) power conversion system (Z-T-NPC-MLI) with the aid of New Space Vector PWM (SVPWM) scheme. The proposed impedance source (Z-Source) MLI associations the advantages of boosting operations with DC to AC power conversions. There are many MLI Z-Source research papers for concentrating the desired voltage generations with minimal switching and conduction losses. Nevertheless, the reported research on Z-NPC-MLI SVPWM has dealt with reduction of Shoot through (ST) options and voltage boosting operations enhancement; those are does not address the neutral point fluctuation (NPF) problems on the DC-Link. This paper offers improved SVPWM strategies for Zsource NPC-MLI with minimal ST state options. The proposed SVPWM exploits the redundancy switching vector option for both ST and regular switching (non-ST), which offers self-control to NP (DC-link capacitor) balancing. With this benefit of this self- control DC-link capacitors balancing, the inverter able to maintain their output quarter symmetry waveform and henceforth the harmonic spectra for the voltage and current waveform is maintained lesser. The proposed SVPWM for Z-T-NPC-MLI is simulated in MATLAB/SIMULINK 2011.b software environment, and the results confirm the advantages of the proposed inverter and its simplified PWM scheme. The experimentation is also performed for 1kW three-phase Z-T-NPC-MLI system using sparten-6 FPGA processor. The experimental results are confirmed the simulation results.

Keywords- Z Source MLI, T-MLI, Neutral point Diode Clamped, Capacitor balancin.

# I. INTRODUCTION

Renewable energy sources (RESs) are taking the top position in the field of electrical generation. Almost all the countries in the world are encouraging the RESs (mostly PV and wind), due to various reasons like scarcity of the fossil fuels, to reduce the emissions caused via green power generation. Solar energy is the most promising source of energy among the RESs [1].

The inverters are the mandatory segment in the photovoltaic (PV) systems, as the output of any PV system will be DC. Due to this fact, research in the field of inverters has improved a lot in the recent ages. Apart from the PV system, most of the industrial applications require high power/medium power inverters. The two-level inverters ware ran out after the arrival of multilevel inverters (MLIs). The first concept of MLI was proposed by R H Baker [2] in the year 1975. The MLIs enables to attain the high voltage and power ratings without the use of transformers. The advantages of

MLIs are reduced voltage stress, low switching losses and low common mode voltage. The total harmonic distortion (THD) will be reduced with the increase of the number of levels of an MLI. However, the number of levels is limited by constraints like voltage unbalance and circuit complexity. The first three level (3L) MLI was implemented by Nabae [3] in 1981. After 1990s, numerous MLIs topologies are reported in the literature. Nevertheless, these MLIs are grouped in majorly only three types: neutral-point clamped (NPC), flying capacitor (FC) and cascaded H-bridge (CHB). The FC-MLI was invented by Fazel et.al in 1990. It uses a higher number of capacitors to make a level, hence it is requires more protection to ensure the uniform capacitors charging and discharging. The CHB-MLI involves extra isolated DC sources, which is practically impossible with the use of PV based power system. All these pros and cons, the NPC-MLI is a better choice for medium voltage and power applications. The NPC-MLI uses clamping diodes to achieve the levels, which have additional losses. With the elimination of clamping diodes in the NPC MLI L Ma et.al [4] proposed T-Type NPC-MLI in the year 2009, which can also be called as the diode-less NPC-MLI. Here, the switches in single leg of T Type NPC-MLI will be arranged in the form of the alphabet 'T'. The T Type NPC-MLI will have all the reward of the NPC-MLI. Apart from the elimination of the clamping diodes these T Type NPC-MLI have lower switching losses as the switches 2 and 3 will behalf the rating of switches 1 and 4. Due to the low conduction and switching losses T-Type NPC -MLI can achieve an efficiency of 99% [5,6]. Due to all these advantages T Type NPC-MLI will be the best option for the PV applications. However, the DC-link balancing is a considerable element on it.

The output voltage boosting for any MLI topology is not possible without adding DC to DC converter in their input side; this become a main drawback in case of PV applications. Normally, the conventional two stage system structure as DC to DC boosting conversion (through boost converter) and DC to AC (through inverter). This increases the control circuit design complexity and cost. After arrival of impedance source (Z-source) in 2003, the two-stage power conversion is replaced by single-stage power conversion (DC to boosted AC) is becomes popular and recommended for many applications [7]. The reduction in control methods and power switch, the power electronics researchers are started to use Z – source concepts in MLIs and used in many electrical notable application such as wind power generation, HVDC systems etc., In Z-source inverter, the boosting is achieved in front end 'X'- shape elements, formed two though inductors and two

capacitors. The storing the energy in the inductors, it is needs to connect directly with input DC source. Therefore, the inductors need to short through MLI circuit switches. This proposes is called as shoot-through (ST). To organizing the regular switching and ST switching, the Z-source MLI PWM is fairly complex than that of a normal MLI PWM strategy. In carrier PWM methods, the maximum boosting and constant boosting carrier methods are the most acceptable for the Zsource MLI. Similar to MLIs, Z-source too absorbed mainly space vector PWM (SVPWM), since it has a great potential to deal the switching activation with direct control nature [12,13] The ST option for the Z-source NPC-MLIs precisely realized using by using SVPWM with redundant ST options [14]. The proposed method is offered a higher control degree of freedom to vary the output voltage boosting. The similar strategies with minimum ST switching actions are proposed in [15,8], which are mainly focusing to increasing the boosting function of the inverter. The methods are not solving the NP capacitors balancing; hence the output voltage of the inverter is ached with higher THD. The redundancy switching is allows the current flow in the NP in every phase and maintain the zero current at NP [16]. There some interesting paper is published in the literature to ensure the zero NP in every switching cycle interval, which are maintain the self-balancing he capacitors. Considering the NPC-MLI topology types, T-type topology have uses only main control power switches. The clamping diode is totally removed form T-type MLI, and hence it is offered a lesser loss than I-type NPC-MLI [6, 17]. Hence, the concentering the use T-type topology with Z-source is got a more interest in the power converter designer community.

Within this above discussed, the paper proposes a threephase three- level Z-source T-type NPC-MLI and new SVPWM method for voltage-boosting improvement with DC- link NP capacitors balancing without comparing the voltage THD performances. The proposed SVPWM for Z-T-NPC-MLI is simulated in MATLAB/SIMULINK 2011.b software environment, and the results confirm the advantages of the proposed inverter and its simplified PWM scheme. The experimentation is also performed for 1kW three-phase Z-T-NPC-MLI system using sparten-6 FPGA processor. The experimental results are confirmed the simulation results.

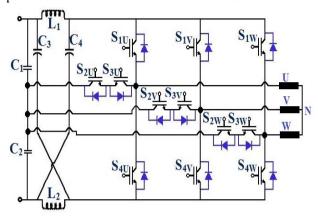

Figure.1 Topology circuit diagram of three-phase three-level Z- source T-NPC-MLI

# II. CIRCUIT DIAGRAM OF THREE-PHASE THREE-LEVEL Z-SOURCE T-NPC-MLI

The three-phase three-level Z- source T-NPC-MLI is as presented in the Figure.1 and the working operation of the inverter can be elucidated with the aid of the single-leg switching shown in Table-1.

| Mode        | State | Switches<br>Triggered      | Diodes Forward<br>biased   | $V_{OUT}$                   |  |

|-------------|-------|----------------------------|----------------------------|-----------------------------|--|

| Non-ST Mode | +1    | $S_{1U} S_{3U}$            | $\mathrm{D}_{\mathrm{3U}}$ | $(V_{DC}/2) + L_1*(di/dt)$  |  |

| Non-S1 Wide | 0     | $\mathrm{S}_{\mathrm{2U}}$ | -                          | 0                           |  |

|             | -1    | $S_{2U} S_{4U}$            | $\mathrm{D}_{\mathrm{2U}}$ | $-(V_{DC}/2)-L_2*(di/dt)$   |  |

| ST Mode     | T     | $S_{1U} S_{2U} S_{3U}$     | -                          | 0 (L <sub>1</sub> Charging) |  |

|             | В     | $S_{2U}S_{3U}S_{4U}$       | -                          | 0 (L <sub>2</sub> Charging) |  |

TABLE 1 Switching table of three-phase three-level Z- source T-NPC-MLI for leg-A

Figure.2 (a) Top Shoot through (b) Bottom Shoot through

From the Table-1, when the switch  $S_1$  and  $S_3$  are 'ON', the positive current flow from the source ( $V_{DC}$ ) to the load. Similarly, the negative current flow form load to source is achieved,  $S_2$  and  $S_4$  is 'ON'. When  $S_2$  is 'ON', the current

# A. Non shoot-through mode:

During the non-shoot through mode the input DC-link voltage ( $V_{DC}$ ) and the inductor voltage together are fed to the MLI, which leads to the boosting operation. The Non-ST mode (regular MLI switching) is divided into three modes [19].

- Mode-1: During this mode, the positive output voltage and positive current is achieved by triggering S<sub>1</sub> and S<sub>3</sub>.

The switch S<sub>1</sub> is only connected between source and load, where the S<sub>3</sub> connecting the NP with the help of D<sub>2U</sub>. This allow the next cycle switching from +1 to 0.

- Mode-2: During this mode, the negative output voltage and negative current is achieved by triggering S<sub>2</sub> and S<sub>4</sub>.

The switch S<sub>4</sub> is only connected between source and load, where the S<sub>2</sub> connecting the NP with the help of D<sub>3U</sub>. This allow the next cycle switching from -1 to 0.

- Mode-3: During this mode, the zero output voltage is achieved by tuned 'ON' switch S<sub>2</sub>. In this mode the current fall to NP and it is should be zero in ideal operation conditions.

# B. Shoot-through mode:

The Z-source MLI shoot-through options are considered to be in three categories, which are call it as, full-ST-state (FST), bottom- shoot-through (BST), top-through(TST) [16].

- FST: During this mode, all the four switches in the inverter leg is 'ON' and proving the direct path to short the inductor with input DC-supply (V<sub>DC</sub>).

- TST: During this mode, the top three switches are turned 'ON' and proving the path to short the inductor. The TST is influenced by positive current on the  $V_{\rm DC}$ .

- ullet BST: During this mode, the bottom three switches are turned 'ON' and proving the path to short the inductor. The TST is influenced by positive current on the  $V_{DC}$ .

fall to NP and it is should be zero in ideal operation conditions. However, due to the non-uniform switching action maintaining the zero current at NP is challenging [1].

#### III. DESIGN OF Z SOURCE NETWORK:

In these sections, the paper takes an opportunity to analysis the Z-source inverter and to calculation of 'X' network elements (L and C) for find the boosting factor (B). Generally in buck-boost DC to DC converter uses the inductor and capacitor with power switch and blocking diode. The blocking diode is avoiding the reverse current flow form the load to source. Similar to buck-boost DC to DC converter, the Z-source inverter uses the L, C, blocking diodes in the positive and negative rail of the DC-bus [6].

As mentioned in Figure-1, the input side X-network (impedance network), and it's consist of two inductors ( $L_1$  and  $L_2$ ) and two capacitors ( $C_3$  and  $C_4$ ). The capacitor and inductor is used in the X-network is equal; therefore the voltage drop across them is related same.

$$V_{L1} = V_{L2} = V_{L} \tag{1}$$

$$V_{C1} = V_{C2} = V_C \tag{2}$$

Throughout the ST mode the voltage across the inductor  $(V_L)$  and capacitor  $(V_C)$  is same and the inductors are charging uniformly and maintain the voltage across the source X- network as  $2V_C$ .

$$V_{I} = V_{C} \tag{3}$$

During the ST;

$$V_i = 2V_C \tag{4}$$

During the non-ST;

$$V_0 = 0 \tag{5}$$

Let consider, T = total switching time,  $T_T$  = TST switching time,  $T_B$ = BST switching time,  $T_0$  = commutation time (zero switching) and  $T_{NST}$ = nearest vector switching used for regular MLI switching []. The switching time T a

combination of the ST and non-ST time periods. The boosting factor (B) is given by

$$B = \frac{T}{T_{NST} - T_0}$$

Where T=T<sub>0</sub>+T<sub>NST</sub>, 20% of the ST time period is selected,

$T_0 = 20\%$  of the time period of one cycle

$$=20\%$$

of  $0.02$

$T_0 = 0.004 \text{ sec}$

$$B = \frac{1}{1 - \left(\frac{2T_0}{T}\right)}$$

$$B = 1.667$$

(6)

In the steady-state conditions, the voltage across the inductor  $(V_L)$  is zero, thus the  $V_L$  over one switching period is given by

$$\frac{\left(V_{DC} - V_{C}\right)T_{NST} + \left(\frac{V_{DC}}{2}\right)T_{T} + \left(\frac{V_{DC}}{2}\right)T_{B}}{T} = 0$$

$$T=T_0+T_T+T \tag{7}$$

By solving equation (7), the voltage across the capacitor ( $V_{\rm C}$ ) is calculated as,

$$V_{c} = (V_{DC}) \left( \frac{1 - \frac{T_{0}}{2T}}{1 - \frac{T_{0}}{T}} \right)$$

$$V = 50V$$

(8)

The output voltage of the Z-source network both in ST and non-ST states are calculated as,

$$V_0 \text{ (Non-shoot through)} = \frac{2V_{DC}}{1 - \frac{T_0}{T}}$$

$$= 250V$$

(9)

$$V_0 \text{ (shoot through)} = \frac{V_{DC}}{1 - \frac{T_0}{T}}$$

$$= 125 \text{V}$$

(10)

Since the voltage across the inductor ( $V_L$ ) is the difference of the  $V_{DC}(\ V_i)$  and capacitor voltage( $V_C$ ). Average inductor current is given by

$$I_{L} = \frac{\text{Total power}}{V_{DC}} \tag{11}$$

The inverter power and DC-link is considering for this proposed Z-T-MLI is 1kW and 100V respectively. Hence From equation (11) becomes,

$$I_L = 10V$$

(12)

Maximum current ripple on the inductors is estimated as 30%; therefore the maximum current ( $I_{LMax}$ ) and minimum ( $I_{LMax}$ ) are calculated as,

$$\begin{split} &I_{_{L\,MAX}}\!=I_{_L}\!+\!(30\%\text{ of }I_{_L}) &\quad I_{_{L\,MIN}}\!=I_{_L}\!-\!(30\%\text{ of }I_{_L})\\ &I_{_{L\,MAX}}\!=\!13\text{ amp} &\quad I_{_{L\,MIN}}\!=\!7\text{ amp} \end{split}$$

Let, the consider voltage variations from the maximum boosted and un-boosted voltages, the inductor value is calculated as,

$$L = \frac{V * T_0}{I_{LMAX} - I_{LMIN}}$$

(13)

Form the 1.2% voltage ripple is assumption; the capacitor value is calculated as.

$$C = \frac{I_L T_0}{\Delta V_C}$$

$$C = 333.33 \mu F$$

(14)

# IV. PROPOSED SVPWM SCHEME FOR Z-T NPC MLI

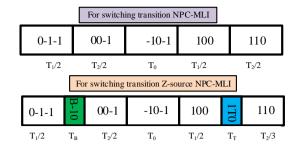

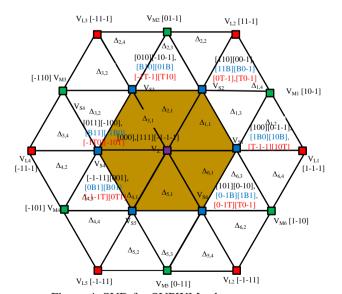

The Z-source MLI SVPWM schemes differ from MLI, only by adding the ST-switching states. This is because, Z-Source NPC-MLI needs ST vectors to charge the inductors present in Z-network in Figure-.1In three-phase three-level Z-source MLI SVPWM uses 54 ST-states, which are connected with 27 regular switching event of MLI and providing the zero neutral-point current in every switching , which allow the DC-link capacitors balancing. However, due to the large switching ST, the inverter suffered with large switching losses which affect the inverter efficiency. In this section, explains the switching method and its self-control option to the capacitor balancing. The proposed method uses the TST and BST with regular MLI switching sequentially for considering the NP balancing.

# A. Proposed ST option:

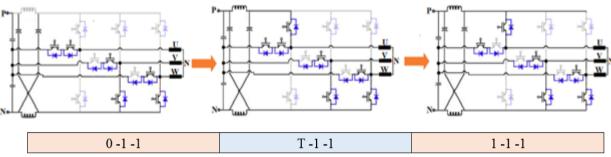

To achieve the minimal switches options between two adjacent states, the nearest three vector (NTV) switching sequence is adopted in SVPWM. The NTV is uses the nearest three switching choice and providing the three-phase current to the NP uniformly. For example; when the reference vector  $(V_{ref})$  positioned in sub-triangle, ' $\Delta_{12}$ ' in sector-1, the switching states are altered from (0-1-1) to (00-1). In this circumstances, the U phase switching state is transformed from {OFF, OFF, ON, ON} through {OFF, ON, ON, ON} to {OFF, ON, ON, OFF} to create BST to charge the inductor, L<sub>2</sub>. Here, the four switches are taken for the lag-U (U-phase). During the switching states from (100) to (110) using the NTV method. In this situation the U-phase switching state is transformed from {OFF, ON, ON, OFF} through {ON, ON, ON, OFF} to {ON, ON, OFF, OFF} to create top-ST to charge the inductor L<sub>1</sub>. After the end of STs, the inductor voltage (V<sub>L</sub>) is added with input voltage (V<sub>DC</sub>) and this boosted voltage (2V<sub>C</sub>≈2V<sub>DC</sub>) will appear at the inverter input terminals and MLI will convert the boosted-voltage into AC output voltage. Figure.3. illustrations the switching conversion for  $\Delta_{12}$  in sector-1. Similar, in all six sectors TST and BST are used with NTV and boosting the input voltage  $V_{DC}$ .

Figure.3 switching transition in linear modulation region for NPC-MLI and Z-source NPC-MLI

In the proposed SVPWM the ST operation is done only with the short vectors to achieve the TST and BST. Furthermore, the proposed SVPWM is fashioned based on the nearest three vector (NTV) switching approach [11], which ensures the circulation current flows in the capacitors. This will improve the quality of the shape of the output wave (quarter symmetry). In the simulation session the effect of capacitors balancing is discussed for both non-NTV and NTV schemes.

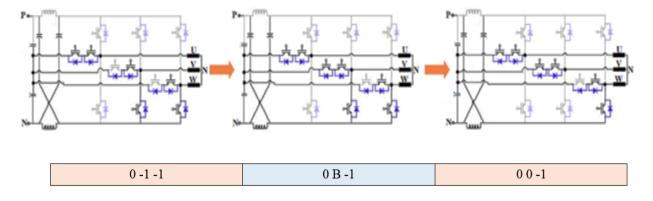

#### B. On-time calculation:

Generally the on-timings are calculated using the NTV scheme [13] in a triangle where the reference vector is located. In (15)-(18) are given the duty cycles for ST vectors and non-ST vectors.

The basic target vector with respect to volt-sec is

$$\begin{aligned} V_{\rm ref} &= T_1 V_1 + T_2 V_2 + T_0 V_0 \\ \text{Here, } T_1 &= T_s (V_{\alpha o}^s - V_{\beta o}^s / \sqrt{3}); T_2 &= T_s (V_{\beta o}^s / h; \\ T_0 &= T_s - T_1 - T_2. \end{aligned} \tag{15}$$

In BST based triangle ST periods are created by splitting the on-timing of  $T_{\rm 0}$ .

$$T_0 = T_T + T_B + T_{0(active)}$$

(16)

Figure.4. SVD for SVPWM scheme

In TST based triangle ST periods are created by splitting the timing of  $T_1$  and  $T_2$ , since the ST creation in medium vector will disturb the inverter pole voltage.

$$T_1 = T_T + T_{1(active)} \tag{17}$$

$$T_2 = T_B + T_{2(active)} \tag{18}$$

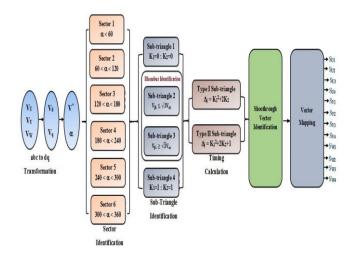

# C. SVPWM for the Z-MLI SVPWM:

Firstly, the three-phase voltage vectors are converted to two-phase using Park's transformation. The sector number  $S_i$  and angle in each sector  $\gamma$  is found by using the angle of the  $V_{ref}$  (0). Each sector will be having four sub-triangles. If the  $V_{ref}$  lies in the sub-triangle 0 and 3 can be found easily by calculating rhombus calculations are to be performed using the slope of the reference vector. In the calculation of the sub-triangle, the Z-source SVPWM uses the published paper logic [13]. Once the sub-triangle number is identified, the ST vectors should be identified. Once the ST switching vectors are identified, the total on-time period should be split for ST and non-shoot-through operations.

# Advantages of New SVPWM scheme

- Uses only 24 ST switching vectors, which reduces the complexity.

- The redundant technique on time calculation is easy and leads to easy timing calculation and hardware implementation.

Figure.5. Proposed SVPWM switching pulse generation

# V. SIMULATION RESULTS & ANALYSIS

The performance of the Z-source SVPWM for Three-phase three-level Z-T NPC-MLI with an RL load is studied through MATLAB/Simulink 2013.a simulation. The input DC-link voltage is sustained as 100V with the aid of DC. The values of capacitance and inductance in the Z-source network are  $340\mu F$  and 10 mH. The IGBT with a parallel diode for commutation is used as the switch in the circuit, the internal

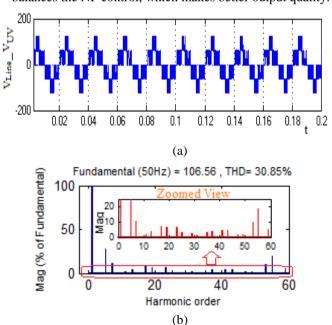

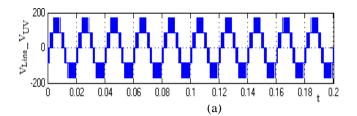

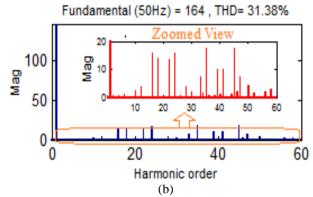

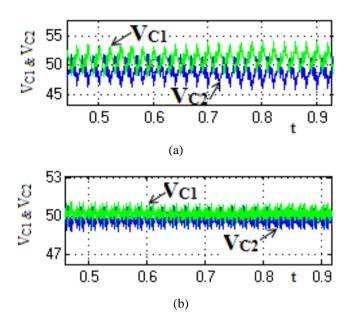

resistance of IGBT is considered as  $1m\Omega$  and snubber resistance is  $10u\Omega$  [15]. Two equal capacitors are considered across the supply to split the supply voltage (VDC) into two equal (V<sub>DC</sub>/2) shares and to create a neutral-point voltage. The B is fixed to be 1.67. As a result for an input DC supply,  $V_{DC}$ =100V, theoretical output should be 142V in linear modulation range. The Figure.6. shows the line voltage (V<sub>Line</sub>) and THD spectra at under modulation, M<sub>a</sub>=0.6. Here, the V<sub>Line</sub> and percentage of THD is observed to be 106.56V and 14.85%. The  $V_{Line}$  will be very low at the lower modulation indices because the on-time of the MLI will be less during this period, then the V<sub>Line</sub> gradually increases with the increase of the M<sub>a</sub>. Next, the proposed SVPWM is tested for extreme of linear modulation range (m<sub>a</sub>=0.9) as shown in the Figure.7. At this Ma, the inverter delivered its maximum output link voltage as 164V with considered harmonics spectra of 31.38%. Based on the results it is evident that the proposed PWM, delivers the maximum output based on eq.(6). In addition, the proposed PWM output V<sub>line</sub> and its respective % THDs are comparatively better when compared to the reported methods [6,11]. The main reason for the improvement of the  $V_{line}$  in Z-T NPC-MLI is due to employment of T-Type NPC-MLI rather than conventional NPC-MLI, which reduces the conduction losses to a better extent. The harmonics spectra and waveform quality improved by the selection of proper ST time periods by using the proposed SVPWM scheme. Figure.8 presents the different  $M_a$  performances for  $V_{line}$  and %THD of Z Source TMLI. Due to the redundancy and NTV switching logic, the link capacitors (C<sub>1</sub> and C<sub>2</sub>), whereas regular Z-SVPWM will not bother about the DC-link balancing. Figure.9. illustrates the capacitor balancing proposed-NTV based SVPWM and regular SVPWM. Based on the results, it could be deduced that the proposed scheme not only uses less ST States, but also balances the NP control, which makes better output quality.

Figure.6 Simulation results for  $m_a$ =0.6; (a). line voltage( $V_{\text{LINE}}$ ), (b)  $m_a$ =0.5

Figure.7 Simulation results for  $m_a$ =0.8; (a). line voltage( $V_{LINE}$ ), (b)  $m_a$ =0.9

TABLE II- SIMULATION RESULT COMPERISION OF REGULAR SVPAM AND PROPOSED SVPWM FOR DIFFERENT Ma

| $M_a$    |            | 0.2   | 0.4   | 0.6    | 0.8   | 0.907 |

|----------|------------|-------|-------|--------|-------|-------|

| Con      | $V_{LINE}$ | 40.7  | 69.5  | 102.1  | 136.7 | 156.9 |

| SVPWM    | %THD       | 64.37 | 56.82 | 57.26  | 56.82 | 57.59 |

|          | %NPF       | 2.7   | 2.7   | 3.5    | 4.7   | 6.3   |

| Proposed | $V_{LINE}$ | 41.2  | 70.9  | 106.56 | 142.1 | 164   |

| SVPWM    | %THD       | 34.37 | 36.82 | 30.85  | 31.82 | 31.38 |

|          | %NPF       | 2.7   | 2.7   | 2.8    | 2.9   | 2.9   |

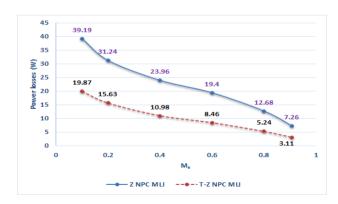

# Conduction Losses comparison

The Total conduction losses of the Z-T-NPC-MLI and conventional Z-NPC-MLI are calculated and plotted in Figure.9. for various  $M_a$ . These values are verified with the simulated tests. From the graph, it can be seen that the conduction losses are low throughout the operating value of  $M_a$ , which leads to better of Z-T-NPC-MLI.

Figure.8 Conduction losses comparison of Z-T NPC-MLI and conventional Z Source NPC-MLI

Figure. 9 Z-T NPC-MLI DC-link capacitors balancing simulation results; (a) Conventional ZSVPWM,(b) proposed ZSVPWM.I

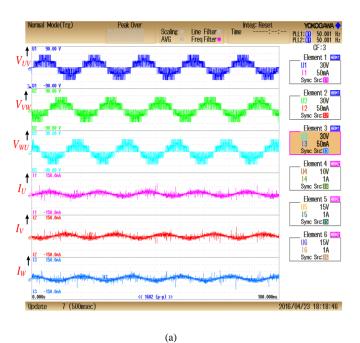

# VI. EXPERIMENTAL ANALYSIS

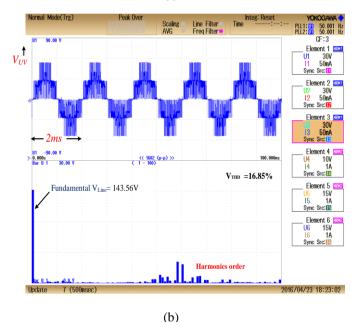

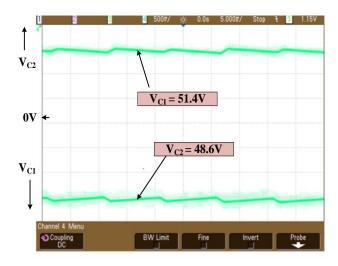

The simulation performance of the proposed SVPWM for Three phase - three level Z-T NPC MLI with an RL load is examined through FPGA based 1Kw Z-T NPC MLI simulation study was conducted. The input DC-Link voltage is maintained as 100V with the help of direct DC Source from 0 to 200 V RPS. The values of capacitance and inductance in the Z source network are 340µF and 10 mH respectively. The IGBT with a parallel diode for commutation is used as the switch in the circuit, the internal resistance of IGBT is considered as  $1m\Omega$  and snubber resistance is  $10\mu\Omega$  [22]. Two equal capacitors are considered across the supply to split the supply voltage into two equal halves and to create a neutral point. The boosting factor is considered to be 1.67. As a result, for an input DC supply voltage of 100V, theoretical output should be 142V in linear modulation. The Figure. 10, shows the line voltage (V<sub>Line</sub>) and THD spectra at under modulation, M<sub>a</sub>=0.9. Here, the V<sub>Line</sub> and percentage of THD is observed to be 143.56V and 16.85%. Due to the redundancy ST switching logic, the DC-link capacitors ( $C_1$  and  $C_2$ ), is maintained their balancing and maintaining the NP. The Figure.11 (a) and (b) show the DC-link capacitors  $V_{C1}$  and  $V_{C2}$  voltages. Based on the results, it could see that the proposed SVPWM balancing the capacitors closely and ensuring the symmetry voltage waveform.

Figure. 10 Experimental line voltage ( $V_{LINE}$ ), and its respective THD spectra at  $m_a$ =0.907.

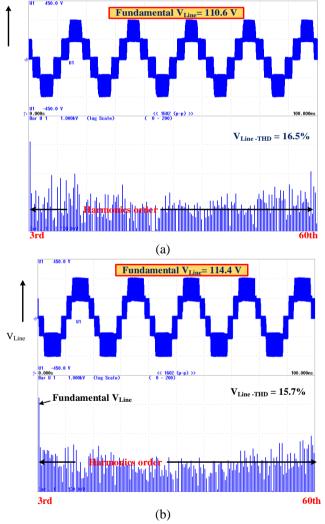

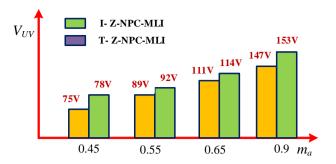

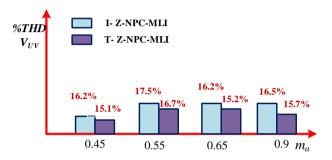

From the experimental results, it is evident that the proposed SVPWM for Three-phase three-level Z- source T NPC-MLI gave a similar performance to simulation result obtained. The proposed Z-source SVPWM is compared with I-type NPC-MLI and T-NPC-MLI and the results are listed. For this comparisons, the both the MLIs are operated in m<sub>a</sub> range from 0.4 to 0.8.

Figure. 11 Experimental Z-T NPC-MLI DC-link capacitors balancing for proposed ZSVPWM.I

Figure.12 Experimental line voltage ( $V_{LINE}$ ), and its THD  $m_a$ =0.907;(a)Z-source I NPC-MLI,(b)Z-source T NPC-MLI.

Figure.13 Experimental results; line voltage comparison between I-type and T type Z-source NPC-MLI

Figure.14 Experimental results; line voltage THD comparison between I-type and T type Z-source NPC-MLI

The inverters input voltages are fixed for 100V for this comparative study. Figure 12.(a) and 12.(b) are shows experimental results line voltage and its THD performance comparisons between I-type and T type Z-source NPC-MLI. From the results T-Z-source NPC-MLI show the better performance then I-type MLI. The fundamental line voltages are more in all the range of modulation Indies. The main reason for the improvement of the V<sub>line</sub> in Z-T NPC-MLI is due to employment of T-Type NPC-MLI rather than conventional NPC-MLI, which reduces the conduction losses to a better extent. The efficiency of the inverter calculated for both I-type and T type Z-source NPC-MLI from the conduction losses. The T type Z-source NPC-MLI efficiency is estimated as 94.4% at m<sub>a</sub>=0.9, whereas I-type has 91.3%. Based on the experimentation results and analysis, the T type Z-source NPC-MLI is provides a better with help of proposed Z-source SVPWM with minimal ST switching events.

# **V.CONCLUSION**

A novel Z-T NPC MLI is implemented using the new SVPWM scheme and operated in the entire modulation region both in shoot through mode and non-shoot through mode. This proposed SVPWM scheme uses redundant technique, which provides the equal switching stress to all the phases which improves the performance of the inverter for long operations. Even though with the use of less

number of shoot through vectors more boosting factor of 1.67 is achieved for the inverter which reduces the complexity in the switching of the inverter. The conduction losses calculation is done for Z-T NPC-MLI and conventional Z source NPC-MLI. The conduction losses of the Z-T NPC-MLI are much lower when compared to conventional Z source NPC-MLI; this indicates that the designed Z-T NPC-MLI is the most efficient Z source inverter. The simulation and experimental results of threelevel Z-T NPC-MLI inverter fed RL load with various modulation indices implemented are MATLAB/SIMULINK 13.a and hardware realization is done using improved FPGA implementation. The novel Z-T NPC MLI has better boosted line voltage and THD profile when compared to the conventional Z source NPC0MLI discussed by various authors in the literature.

- As redundant scheme is used in SVPWM scheme the switching stress will be uniform, thus reducing the complexity in timing calculations and can be implemented in hardware easily.

- Only 24 shoot through states out of 54 possible shoot through states are used, which reduces the complexity in the SVPWM scheme.

- Improved FPGA implementation enables the advantage of less device utilization. Therefore, the device memory saved by using improved FPGA implementation can be used for the other purposes like the developments in the scheme or closed loop operation.

#### **REFERENCES**

- [1] C. Bharatiraja · S. Jeevananthan, and R. Latha, "FPGA based practical implementation of NPC-MLI with SVPWM for an autonomous operation PV system with capacitor balancing," International Journal of Electrical Power & Energy Systems., vol. 61, no. 1, pp. 489–509, Oct. 2014.

- [2] Baker R. H., Bannister L. H. 'Electric power converter', U.S. patent 3867 643, 1975.

- [3] Nabae A., Takahashi I. and Akagi H., "A New Neutral-Point-Clamped PWM Inverter," IEEE Transactions on Industry Applications, vol. 17, no. 5, pp.518-523, 1981.

- [4] L. Ma, T. Kerekes, R. Teodorescu, X. Jin, D. Floricau, and M. Liserre, "The high efficiency transformer-less PV inverter topologies derived from NPC topology," in Proc. 13. European Conf. Power Electronics and Applications, 2009, pp. 1–10.

[5] Mario Schweizer, Johann W Kolar, "Design and

- [5] Mario Schweizer, Johann W Kolar, "Design and Implementation of a Highly Efficient Three-Level T-Type Converter for Low-Voltage Applications," IEEE Transactions on Power Electronics, vol. 28, no. 2, February 2013.

- [6] Yong Wang, W. W. Shi, N. Xie, C.M.Wang, "Diode-Free T-Type Three-Level Neutral-Point-Clamped Inverter for Low-Voltage Renewable Energy System," IEEE Transactions on Industrial Electronics, vol. 61, no. 11, November 2014

- [7] Fang Zheng Peng, "Z-Source Inverter," IEEE Transactions on Industry Applications, vol. 39, no. 2, March/April 2003.

- [8] Francis BoafoEffah, Patrick Wheeler, Jon Clare, Alan Watson, "Space-Vector-Modulated Three-Level Inverters with a Single Z-Source Network," IEEE Transactions on Power Electronics, Vol. 28, No. 6, June 2013.

- [9] P. C. Loh, D. M. Vilathgamuwa, Y. S. Lai, G. T. Chua, Y. W. Li, "Pulse width modulation of Z-source inverters", IEEE Trans. Power Electron., vol. 20, no. 6, pp. 1346–1355, Nov. 2005.

- [10] P. C. Loh, F. Gao, F. Blaabjerg, "Topological and modulation design of three-level Z-source inverters," IEEE Transaction Power Electronics, Vol. 23, No. 5, pp. 2268–2277, Sep. 2008.

- [11] B. Chokkalingam, S. Padmanaban, P. Siano, Z. Leonowicz, and A. Iqbal, "A hexagonal hysteresis space vector current controller for single Z-source network multilevel inverter with capacitor balancing," 2017 IEEE International Conference on Environment and Electrical Engineering and 2017 IEEE Industrial and Commercial Power Systems Europe (EEEIC / I&CPS Europe), Jun. 2017.

- [12] Gupta, A.K., Khambadkone, A.M., "A Space Vector PWM Algorithm for Multilevel Inverters based on Two-level Space Vector PWM," IEEE Transactions on IEEE Transactions on Industrial Electronics, vol. 53, no. 5, pp. 163-171, 2006.

- [13] C. Bharatiraja, S. Jeevananthan, and J. L. Munda, "A Timing Correction Algorithm-Based Extended SVM for Three-Level Neutral-Point-Clamped MLI in Over Modulation Zone," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 6, no. 1, pp. 233–245, Mar. 2018.

- [14] Poh Chiang Loh, FredeBlaabjerg, Chow Pang Wong, "Comparative Evaluation of Pulsewidth Modulation Strategies for Z-Source Neutral-Point-Clamped Inverter" IEEE Transaction Power Electronics, vol. 22, no. 3, pp. 1005–1013, May 2007

- [15] C. Bharatiraja · S. Jeevananthan, J.L. Mundaand R. Latha, "Improved SVPWM vector selection approaches in OVM region to reduce common-mode voltage for three-level neutral point clamped inverter," International Journal of Electrical Power & Energy Systems., vol. 79, no. 1, pp. 285–297, Oct. 2014.

- [16] B. Chokkalingam and J. L. Munda, "Simplified SVPWM for Z Source T-NPC-MLI including neutral point balancing," 2016 IEEE Symposium on Computer Applications & Industrial Electronics (ISCAIE), May 2016.

- [17] D. Leuenberger and J. Biela, "Comparison of a Soft Switched TCM T-Type Inverter to Hard Switched Inverters for a 3 Phase PV Grid Interface," 15th International Power Electronics and Motion Control Conference, EPE-PEMC 2012 ECCE Europe, Novi Sad. Serbia.

- [18] Rodriguez, J.S., Lai, F.Z. Peng, "A survey on the neutral point clamped inverters," IEEE Transactions on Industrial Electronics, vol. 57, no. 7, July 2010, pp.2219–2230.

- [19] Ying-Yu, T., and Hau-Jean, H., "FPGA Realization of Space-Vector PWM Control IC for Three-Phase PWM Inverters," IEEE Transactions on Power Electronics, vol.12, no.6, pp.953-963, 1997

- [20] Hew, W.P., Ooi, C.P., and Rahim, N.A., "Realization of Space Vector Modulation Technique in a Single FPGA Chip for Induction Motor Drive," *Proceedings of IEEE Conference Electron Devices and Solid-State Circuits (EDSSC '05*), pp.817-820, 2005.