# THE CONTRIBUTION OF DIRECT TORQUE CONTROL WITH APPLICATION OF FUZZY LOGIC ON THE PERFORMANCE OF A MULTI-LEVEL INVERTER FED INDUCTION MACHINEWITH A FAULT TOLERANCE

#### BENAOUDA O & BENDIABDELLAH A,

Laboratoire De Development Des EntrainementsElectrique (LDEE), Diagnostic group, Faculty Electrical Engineering, Electronics Department, University of Science and Technology of Oran, Oran, Al M'naouar, Algeria

E-mail: <u>benaouda.omar@yahoo.fr</u>E-mail: <u>bendiazz@yahoo.fr</u>

Summary - Today it is possible to obtain induction machines performances similar to those of dc machines through the mastering of power electronics and control. Moreover, there are new methods of control for sensor less speed traction-type applications already studied particularly those related to the Direct Torque Control technique (DTC). This study consists at optimizing the three-level DTC algorithm fed from an NPC structure multilevel inverter with fault tolerant using a reconfigurable redundant spare arm to increase the average value of the torque. The results obtained in the DTC are further improved by applying the technique of fuzzy logic.

Keywords—Multilevel Inverter, DTC, NPC, Fault tolerance, Fuzzy Logic.

## I. INTRODUCTION

These last years, the use of multilevel inverters has largely increased in many industrial applications [1]. The multilevel voltage source inverter can be classified into three major circuit topologies, namely, diode clamped multilevel inverter, commonly known as three-level Neutral-Point-Clamped (NPC) voltage source inverter, which was first introduced by Akagi et al. in 1981[2], flying capacitor inverter originated from conventional two-level inverter by adding capacitors to the series connected switches, cascaded H-bridge inverter, which is composed of a series of single-phase H-bridge power cells [3]. The orientation to the multilevel inverter is due to the various advantages of these topologies,like operating under high dc-bus voltages, reduction in output voltage harmonics [4], low voltage stress on power switches [5], and low dv/dt of output voltage [6]. Fault-tolerant capability of power electronics equipment is extremely important to safety-critical applications where continuous drive operation must be insured. Obviously, this capability is expensive and can be justified only for applications with high reliability requirements where risk to human life is substantial, damage of the environment or high costs arising from downtime. In many critical industrial applications, multilevel inverters are used as induction machine drive. The failure of one ormore IGBT module of this drive can causethe total shut down of the system. One of the solution proposed to handle this problem, is the reconfiguration of the faulty inverter [7][8][9]. The DTC widely applied for induction

machine control [10], has been applied in the fault tolerant control [11].

In this paper, a fault control strategy is proposed for induction machine drives fed with three-level NPC converter by applying the direct torque control. The proposed reconfigured multilevel NPC inverter is first described. The DTC technique including the inverter system is then dealt with. Wethen move to the study of the system under various faults such as:1) switch short in a phase leg, 2) switch open in a phase leg, 3) phase leg open. The post-fault performance of each drive is analyzed and test results are presented for the reliability of tolerance and susceptibility of fault.

#### II. PROPOSED TOPOLOGY

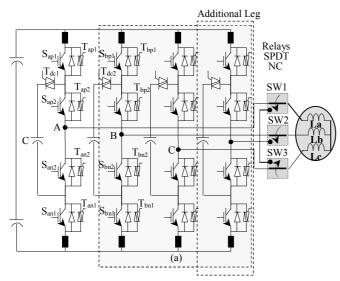

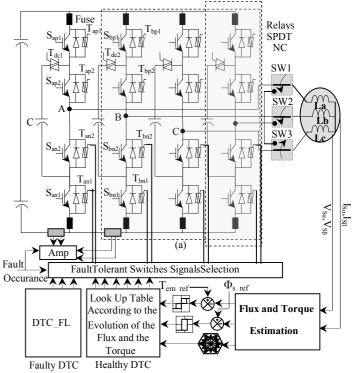

The additional phase leg fault-tolerant inverter topology consists of four inverter legs and a standard three-phase machine, as shown in Fig. 1. In this topology, each phase leg contains a series of two fuses at the terminal upper and lower power devices to isolate the leg for shoot through faults similar to additional leg topology. Each phase leg contains a series of two fuses at the upper and lower power devices terminals to isolate the leg for shoot through faults similar to additional leg topology. Each phase winding of the machine is connected to a normally closed side of an SPDT electromechanical relay, while the open terminals of three relays are tied to the center point of the inverter fourth leg, as shown in Fig. 1. Under normal operation, the fourth leg is not activated. [12][13].

If a fault occurs in any one of the inverter phase legs, that leg is isolated by means of the relay, and the phase winding is connected to the additional phase leg and activated.

This topology provides rated post-fault power without the overrating of power devices, and the output torque is similar to that of the pre-fault operation without excessive torque ripple, as will be shown in Section III via simulation work. It consists of sixteen MOSFETs, eight fuses, three relays, six terminals connections, and a filter capacitor.

The flying capacitor multilevel inverter is another type of multilevel inverter that can tolerate switch faults through reconfiguration of the inverter switching pattern [14].

Fig. 1. Schematic of three leg of a flying capacitor multilevel (three-level) inverter with isolating capability.

of the fault-tolerant three-level flying capacitorinverter are shown. Assuming that Saplis a faulty switch, it canbe bypassed using the parallel low-frequency switch, T<sub>bp1</sub>.At the same time, the corresponding switch in the opposite polarity, Tbn1is forced to turn on, and T<sub>dc2</sub>is turned off to separate the related dc-bus capacitor branch. Accordingly, the remaining switches,  $S_{bp2}$  and  $S_{bn2}$  can operate like an inverter leg in conventional two-level inverters. The most remarkable feature of this design is that it does not require an auxiliary leg in addition to tolerating a single-switch fault per phase without reducing the quality of the generated three-phase output voltagesshown in part(a). The disadvantage of this three-level inverter is that, S<sub>bp2</sub> and S<sub>bn2</sub> must hold twice the normal voltage magnitude during the post-fault situation. As the number of levels (or cells) increases, the number of possible alternative switching patterns for the same output voltage increases. For example, in a four-level flying capacitor inverter, the number of levels in the output voltages can remain constant after isolating a single switch per phase [14].

# II. FAULT TOLERANT DTC STRATEGY

## II. 1. DTC Principle

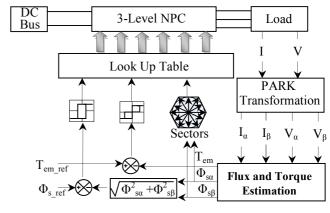

Direct Torque Control is based on control of both torqueamplitude and stator flux amplitude of the machine byapplying appropriate stator voltage vectors using twohysteresis regulators. The control scheme principle is described in Fig.2. Stator flux estimation is performed using stator current and voltage measurements and stator voltage equation in  $\alpha$   $\beta$  reference frame:

$$\emptyset_s = \sqrt{\emptyset_{s\alpha}^2 + \emptyset_{s\beta}^2} \tag{5}$$

Where:

$$\emptyset_{s\alpha} = \int (V_{s\alpha} - R_s I_{s\alpha}) dt \tag{6}$$

$$\phi_{s\beta} = \int (V_{s\beta} - R_s I_{s\beta}) dt \tag{3}$$

The electromagnetic torque is calculated as:

$$T_{em} = P.(\phi_{s\beta}.I_{s\alpha} - \phi_{s\alpha}.I_{s\beta})$$

Where *P* is the number of poles. (4)

Fig.2 shows the different blocs of the DTC strategy.

Fig. 2.DTC strategy.

#### II.2. SELECTION OF THE VOLTAGEVECTOR Vs

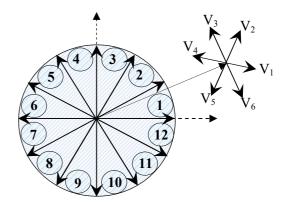

The choice of the vector Vs depends on the location of the  $\emptyset_s$  in the referential (S), on the desired variation of the module  $\emptyset_s$ , on the desired variation torque and on the direction of rotation of  $\emptyset_s$ . The evolution space of  $\emptyset_s$  in (S) is divided into twelve space areas, with i = [1,12] see Fig.3.

Fig.3. Representation of 12 divisions of the complex plane.

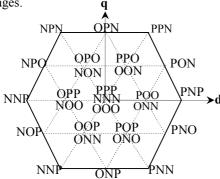

The voltage vectors associated with switching states are:

| Vector | Symbol                                          |

|--------|-------------------------------------------------|

| ZVV    | (P P P),(O O O),(N N N)                         |

| MVV    | (P O N),(O P N),(N P O),(N O P),(O N P),(O N P) |

| LVV    | (P N N),(P P N),(N P N),(N P P),(N N P),(P N P) |

| USVV   | (P O O),(P P O),(O P O),(O P P),(O O P),(P O P) |

| LSVV   | (O N N),(O O N),(N O N),(N O O),(N N O),(O N O) |

Tab. 1. Voltage vectors associated with switching states of 3-levelinverter.

The table shows that there are 27 states of the inverter switching. Under these conditions, there will be 19 different vector voltages.

Fig.4. Space voltage vector diagram in normal condition.

Figure 4 shows that the voltage vectors are classified into four groups according to their modules. These are:

-ZVV group, the zero voltage vectors:  $V_0$ . -SVV group, the small voltage vectors:  $V_1, V_4, V_7, V_{10}, V_{13}, V_{16}$ . -MVV group, the mean voltage vectors:  $V_3, V_6, V_9, V_{12}, V_{15}, V_{18}$  -LVV group, the large voltage vectors:  $V_2, V_5, V_8, V_{11}, V_{14}, V_{17}$ .

## III.ELABORATION DE LA TABLE DE COMMUTATION AVEC LES 4 GROUPES DES VECTEURS TENSION

| N    |      |       |                |                |                  |                 |       |                |                             |       |       |                  |       |

|------|------|-------|----------------|----------------|------------------|-----------------|-------|----------------|-----------------------------|-------|-------|------------------|-------|

| cflx | ccpl | N     | N              | N              | N.               | N               | N,    | N              | N,                          | N     | N     | N                | N     |

|      | 2    | V     | . V            | Į V            | ξ V              | $V_{11}$        | V     | V.             | $V_1$                       | $V_1$ | V     | V <sub>z</sub>   | V     |

|      | 1    | V     | Į V            | Έ Ι            | γ <sub>ε</sub> V |                 | V     | V              | $V_1$                       | $V_1$ | V     | $V_1$            | V     |

| 1    | 0    | V     | , V            | (V             | c V              | $_{0}V_{0}$     | V     | <sub>c</sub> V | C V                         | V     | V     | V                | V     |

|      | -1   | $V_1$ | $V_1$          | V              |                  | $_{3}V_{6}$     | V     | , V            | , V                         | $V_1$ | $V_1$ | $V_1$            | $V_1$ |

|      | -2   | $V_1$ | V              | <sub>2</sub> V | <sub>2</sub> V   | V <sub>5</sub>  | V     | į V            | $V_{\epsilon}$ $V_{1}$      | $V_1$ | $V_1$ | $V_1$            | $V_1$ |

|      | 2    | V,    | V.             | V              |                  | V <sub>10</sub> | $V_1$ | $V_1$          | V                           | V     | $V_1$ | V                | V     |

|      | 1    | V     | <sub>4</sub> V | , V            | , V              | $V_{10}$        | $V_1$ | $V_1$          | V                           | $V_1$ | $V_1$ | V                | V     |

| 0    | 0    | V     | c V            | c V            | ( V              | $_{0}V_{0}$     | V     | V              | <sub>t</sub> V <sub>t</sub> | V     | V     | V <sub>c</sub>   | V     |

|      | -1   | V     | <sub>C</sub> V | , V            | ιV               | $_{c}V_{0}$     | V     | ( V            | , V                         | V     | V     | . V <sub>c</sub> | V     |

|      | -2   | V     | $V_1$          | $V_1$          | V                | $_{1}V_{1}$     | V     | <sub>z</sub> V | 4 V                         | , V   | $V_1$ | $V_1$            | $V_1$ |

| -1   | 2    | V     | <sub>E</sub> V | į V            | V                | $V_{14}$        | $V_1$ | $V_1$          | V                           | V     | V     | ٧                | V     |

|      | 1    | V     | , V            | y V            | V                |                 | V     | V              | $V_1$                       | V     | V     | $V_{\epsilon}$   | V     |

|      | 0    | V     | V              | , V            | <sub>c</sub> V   | $_{0}V_{0}$     | V     | ( V            | , V                         | V     | V     | V                | V     |

|      | -1   | $V_1$ | $V_1$          | V              | V                | $V_{18}$        | V     | V              | V                           | Ve    | V     | Vç               | V     |

|      | -2   | V     | $V_1$          | V              |                  | $V_2$           | V     | . V            | . V                         | V     | $V_1$ | $V_1$            | $V_1$ |

Tab .2 Look up table for twelve sectors before failure.

## IV. BASED FUZZY LOGIC DTC

## A. Based principle of fuzzy logic

Fuzzy logic is a method of treatment of uncertainties and is intended for the representation of imprecise knowledge. It is based on current linguistic terms such as: small, large, medium.... etc... It allows intermediate values between right and wrongand admits overlap between them. [15][16].

## B. Control Variable

Control rules can be expressed in terms of input variables and outputs as follows: R<sub>i</sub>: if  $\epsilon_c$  is A<sub>i</sub> and  $\epsilon_{\phi s}$  is B<sub>i</sub>, and  $\Theta_s$  is C<sub>i</sub> then n is N<sub>i</sub> where A<sub>i</sub>, B<sub>i</sub>, N<sub>i</sub> are the fuzzy sets [17].

The treatment of these rules shall be made by the method of the least Mamdani expressed by:  $\mu_{Ri}(n)=\min(\alpha_i,N_i)$ ; With:

$$\alpha_{i} = \min(\mu_{Ai}(\epsilon_{C}), \mu_{Bi}(\epsilon_{\phi}), \mu_{Ci}(\Theta_{S})) \tag{7}$$

## C. Switching table for (DTC LF)

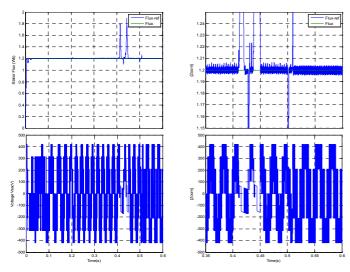

The following tables are similar. Simulation results of stator current, stator flux, electromagnetic torque and output voltage for the case of a three-phase IM with 10Nm load at t=0.3s. variables errors: " $\epsilon_{\phi}$ "flux error, " $\epsilon_{c}$ "Torque errors and " $\epsilon_{\phi}$ "flux position.

| $\epsilon_{\phi}$ | LS      | NS      | NL               | PS           | LS      | NS             | NL             | PS    | LS      | NS         | NL         | PS                            |

|-------------------|---------|---------|------------------|--------------|---------|----------------|----------------|-------|---------|------------|------------|-------------------------------|

| P                 | $V_{5}$ | $V_1$   | $V_2$            | $V_2$        | $V_1$   | $V_1$          | $V_2$          | $V_3$ | $V_1$   | $V_2$      | $V_3$      | $V_3$                         |

| N                 | $V_5$   | $V_7$   | $V_4$            | $V_3$        | $V_6$   | $V_5$          | $V_4$          | $V_4$ | $V_6$   | $V_0$      | $V_5$      | $V_4$                         |

| P                 | $V_2$   | $V_2$   | V <sub>3</sub> € | $V_4$        | $V_2$   | V <sub>3</sub> | V <sub>4</sub> | $V_4$ | $V_3$   | $V_3$      | $V_{4}$    | $ agreen{Trigonize}     V_5 $ |

| N                 | $V_1$   | $V_6$   | $V_5$            | $V_5$        | $V_1$   | $V_7$          | $V_6$          | $V_5$ | $V_2$   | $V_1$      | $V_6$      | $V_6$                         |

| P                 | $V_3$   | $V_4$   | V <sub>5</sub>   | $V_5$        | $V_4$   | V <sub>4</sub> | $V_{5}$        | $V_6$ | $V_4$   | $V_{5}$    | $V_{6}$    | $V_6$                         |

| N                 | $V_2$   | $V_0$   | $V_1$            | $V_6$        | $V_3$   | $V_2$          | $V_1$          | $V_1$ | $V_3$   | $V_7$      | $V_2$      | $V_1$                         |

| P                 | $V_4$   | $V_{4}$ | $V_{5}$          | $\neg^{V_6}$ | $V_{6}$ | $V_{5}$        | $V_1$          | $V_1$ | $V_{6}$ | $V_{6}$    | $V_{1}$    | $\neg V_2$                    |

| N                 | $V_3$   | $V_2$   | $10^{\Lambda}$   | $V_1$        | $V_4$   | $V_0$          | $V_3$          | $V_2$ | $V_5$   | $V_1^{12}$ | $V_3^{12}$ | $V_3$                         |

Tab .3Table de commutation pour douze secteurs après le défaut.

# III. SIMULATION RESULTS

Fig. 5.Schematic of three leg of a flying capacitor multilevel (three-level) inverter with isolating capability.

The proposed DTC strategy (Fig.5) is tested on a 7.5 kW induction machine.

The simulation parameters are defined as follows: DC bus=500V, torque hysteresis band=10%, flux hysteresis band=10%. Torque and flux references are respectively 10N.m and 1.2Web.

The controller block diagram for this topology is shown in Fig. 5. The normally open terminals of all the SPDT relays SW1–SW3 are connected to the additional phase leg, as shownin Fig. 5. When a fault occurs in a given phase leg, the SPDT relay of that phase isolates the faulted inverter phaseleg and connects the machine phase winding to the additionalleg while steering the gate pulses of the faulted inverter legto the respective power devices of the additional phase leg for postfault operation.

Dans le cas où un défaut sera signalé au niveau du reste dispositif (le bras redondant ou les deux premiers bras sains), à ce moment les relais de SPST reconfigurent l'onduleur de trois niveaux à deux niveaux.

Using this model, the following faults have been simulated additional phase leg.

- 1) switch short-circuit fault in a phase leg;

- 2) switch gate pulse open fault in a phase leg;

- 3) phase leg open fault.

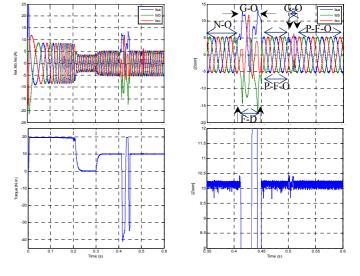

- 1) Switch Short-Circuit Fault in a Phase Leg:In this fault, the bottom switch in phase leg A is shorted, as symbolized in Fig. 5. The performance of the drive during normal operation, faulted condition, and postfault operation is shown in Fig. 6.

The fault is created at t = 0.41 s, and the gate pulse to the upper device is disabled to avoid a shoot through condition. The drive is allowed to continue under faulted condition for 0.05 s, and remediation action is taken by isolating the faulted phase leg A by means of the electromechanical relay SW1 while steering

the gate pulses of the faulted phase leg to respective devices of the additional phase leg inverter. The second fault is creacted at t=0.5s, The drive is allowed to continue under faulted condition for 0.01 s, assuming that  $S_{ap1}$  is a faulty switch, it canbe bypassed using the parallel low-frequency switch,  $T_{bp1}$ . At the same time, the corresponding switch in the opposite polarity,  $T_{bn1}$  is forced to turn on, and  $T_{dc2}$  is turned off to separate the related dc-bus capacitor branch. Accordingly, the remaining switches,  $S_{bp2}$  and  $S_{bn2}$  can operate like an inverter leg in conventional two-level inverters.

The simulation results of phase currents and electromagnetic torque of the machine for this fault under prefault, faulted, and postfault operation is shown in Fig. 6. It is clear that under faultconditions, the drive experiences large torque oscillations as in the previous cases, however, this topology restores normal postfault operation without an inverter overrating, as required in the other two topologies[18].

2) Switch Gate Pulse Open in a Phase Leg: Simulation results of switch gate pulse open in a phase leg are shown in Fig. 6. In this case, large torque oscillations occur during thefault, and the normal postfault operation is restored with theadditional phase leg.

Fig. 6. Simulation results applied to a three-phase IM with 10Nm load at t=0.3s.Stator currents, Stator flux, electromagnetic torque and output voltage. Switch short-circuit fault failure introduced inS<sub>an1</sub>,S<sub>bn2</sub> at 0.41s,0.5srespectively.

Fig. 7. Simulation results of stator current, stator flux, electromagnetic torque and output voltage for the case of a three-phase IM with 10Nm load at t=0.3s. The gate pulse open fault failure introduced in  $S_{an1}, S_{bn2}$  at 0.41s and 0.5s respectively.

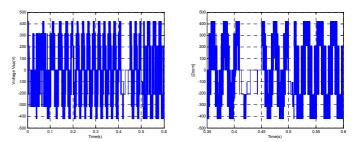

3) Phase Leg Open Faults: Simulation results of a phase leg open fault are shown in Fig. 8. In this case, large torque oscillations also occur during the fault, and the normal post-fault operation is restored by transferring the phase winding from the faulted phase leg to the additional phase leg and activating. Thus, the additional phase leg topology restores normal post-fault operation, which is an important requirement for automotive safety critical systems.

Fig. 8.Simulation results of stator current, stator flux, electromagnetic torque and output voltage for the case of a three-phase IM with 10Nm load at t=0.3s. The phase open fault failure introduced in  $S_{an1}$ ,  $S_{bn2}$  at 0.41s and 0.5s respectively.

| Abbreviation | Meaning              |

|--------------|----------------------|

| NO           | Normal Operation     |

| FD           | Fault Duration       |

| SS           | Switch Sort-Circuit  |

| GO           | Gate pulse Open      |

| PO           | Phase leg Open       |

| PFO          | Post Fault Operation |

Tab .3Table of different fault proposed and abbreviation.

## VI. OTHER FAULTS AFFECTING THE SYSTEM PERFORMANCE

There are several other faults, including dc bus fault and machine winding faults, that can affect the performance of the drive. Though the scope of this paper is not to address the machine faults, the authors would like to provide some information without violating some of the company's proprietary/ confidential information with respect to the mean time between failures of the system, including the following.

- 1) In case of a dc bus fault resulting dc bus over current, the over current limit circuit trips the breaker. For example, dc bus capacitor failure is one such type of fault that occurs commonly.

- 2) To avoid winding faults, machines are built with proper winding insulation, slot liners between winding and the stator core, and phase separators in the slots as well as at the end windings. Providing adequate separation between the lead wire terminals at the connector and potting with insulation compound at the back of the connector minimizes terminal shorts. In low-voltage machines, which in this case is 42 V, the possibility of any machine fault is very remote, which is an order or two magnitudes less than the inverter faults.

The types of machine faults are listed as follows.

- 1) Line–ground fault: it can be minimized by proper slot insulation and impregnation of windings.

- 2) Line-line fault: proper phase separation insulator likeNomex 410 in slots as well as at the end windings minimizes such fault.

- 3) Three-phase terminal short fault: proper spacing and termination of lead wires to the connector and potting

- with insulating resin compound at the back of the connector minimizes such fault.

- 4) Turn-turn fault: by providing additional insulation for the first few turns of the coil of each phase and also providing slot insulation to slightly protrude the stator slots off so that impregnation resign bonds to the stator core minimizes such fault.

## A. Faults Identification

Identification of faults is very important for the fault-tolerant system. Prognostics and diagnostics of the faults in the machine as well as in the inverter are new research topics. Identification techniques, such as wavelets, Kalman filters, and particle filters, are being developed for prognostics of faults in the machine as well as in the inverter based on phase current and voltage measurements to avoid catastrophic failures.

Most of the faults can be identified by phase currents and gatepulses signatures, and necessary actions can be taken to isolatethe faulted component. Over current protection circuit of eachphase can detect some machine faults and trips the main circuitbreaker.

- 1) Phase–ground fault: the ground fault circuit at the inverter detects the deviation in summation of three phase currents and trips the dc bus circuit breaker.

- 2) Line-line fault: a line-to-line fault due to failure of twoupper or lower switching devices of inverter legs connected to different phases or short of two phases near themotor terminal box can be detected by the over currentprotection circuit.

- 3) Gate pulse open fault: the gate pulse not reaching the gate of any switching device of a phase leg can be identified by a flag of the digital logic circuitry. The gate pulse fault of any switching device of a phase leg can be identified by the gate pulse circuitry as well as by the voltage across the device. The faulted leg is isolated, and the healthy additional leg is connected for postfault operation.

# IX. SUMMARY AND CONCLUSION

Three fault-tolerant inverter configurations have been analyzed as to their suitability for control systems.

The simplified additional phase leg topology with mechanical relays was found to be the most cost effective and fault tolerant of the topology examined. This topology uses simple normally closed SPDT mechanical relays to restore normal postfault operation without excessive torque ripple or phase currents.

The performance of this simplified additional leg inverter technology was verified through simulations.

Therefore, for safety of direct torque of control with application artificial intelligence fuzzy logic, the simplified additional phase leg inverter topology with normally closed electromechanical relays is the most cost-effective configuration that has a postfault performance that matches the normal prefault operation. Moreover, it uses conventional threephase machines without the additional phase windings or leadsto provide access to the neutral, as required in the other two topologies.

#### REFERENCES

- [1] J. Rodríguez, J. S. Lai, and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls, and applications," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724-738, Aug. 2002.

- [2] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," IEEE Trans. Ind. Appl., vol. IA-17, no. 5, pp. 518-523, Sep./Oct. 1981.

- [3] J. Rodríguez, J. S. Lai, and F. Z. Peng, "Multilevel inverters: A surveynof topologies, controls, and applications," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724-738, Aug. 2002.

- [4] Mingyao Ma, Lei Hu, Alian Chen, and Xiangning He, "Reconfiguration of Carrier-Based Modulation Strategy for Fault Tolerant Multilevel Inverters" IEEE Trans. Power Electron., vol. 22, no. 5, September 2007.

- [5] Alian Chen, Lei Hu, Lifeng Chen, Yan Deng, and Xiangning He, "A Multilevel Converter Topology With Fault-Tolerant Ability" IEEE Trans. Power Electron., vol. 20, no .2, March 2005.

- [6] Wang Baocheng, Wang Jie, Sun Xiaofeng Wu Junjuan and Wu Weiyang, "Phase Multilevel Inverter Fault Diagnosis and Tolerant Control Technique" EPE-PEMC'06, Portoroz, Slovenia, Aug. 2006.

- [7] E. R. da Silva, W. S. Lima, A. S. de Oliveira, C. B. Jacobina, and H. Razik, "Detection and compensation of switch faults in a three level inverter," in Proc. 37th IEEE Annu. Power Electron. Spec. Conf., Jun. 2006, pp. 1–7.

- [8] J. Li, S. Bhattacharya, and A. Q. Huang, "Three-level active neutral point clamped (ANPC) converter with fault tolerant ability," in Proc. 24th Annu. IEEE Applied Power Electron. Conf., Feb. 2009, pp. 840–845

- [9] S. Ceballos, J. Pou, E. Robles, I. Gabiola, J. Zaragoza, J. L. Villate, and D. Boroyevich, "Performance Evaluation of Fault-Tolerant Neutral- Point-Clamped Converters" IEEE Trans. Ind. Electron., vol. 57, no. 8, Aug. 2010.

- [10] Casadei, D.; Serra, G.; Stefani, A.; Tani, A.; Zarri, L., "DTC Drives for Wide Speed Range Applications Using a Robust Flux-Weakening Algorithm", IEEE Trans. Industrial Electronics, vol. 54, Issue 5, Oct.2007.

- [11] H.BenAbdelghani, A.Bennani, I. SlamaBelkhodja ,"Fault Tolerant DTC Strategy for Induction Machine Drives", JTEA'10, Hammamet, Tunisia, Mar.2010.

- [12] B. A. Welchko, T. A. Lipo, T. M. Jahn, and A. E. Schulz, "Fault tolerant three-phase AC motor drive technologies; a comparison of features, cost, and limitations," in Conf. Rec. IEEE IAS Annu. Meeting, vol. 1, Oct. 2003,pp. 539–546.

- [13] B.Naidu, S.Gopalakrishnan, T. W. Nehl, "Fault tolerant permanent magnet motor drive topologies for Automotive X-By-Wire systems," IEEE Trans. Ind. Appl, vol. 46, no. 5, pp. 0093–9994,March/April 2010.

- [14] K. Xiaomin, K.A. Corzine, and Y.L. Familiant, "A unique fault-tolerant design for flying capacitor multilevel inverter," IEEE Trans. Power Electron., vol. 19, pp. 979 987, 2004.

- [15] S.M. Gadoue, D. Giaouris, J.W. Finch "Artificial intelligence-based speed control of DTC induction motor drives. A comparative study," Electric Power Systems Research.vol. 79, pp. 210–219, 2009.

- [16] Benaouda, O; Bendiabdellah, A.; "La contribution du contrôle direct du couple d'une MAS alimentée par des onduleurs multiniveaux:Application de l'intelligence artificielle (Logique Floue).", seconde international Conférence on Power Electronics and Electrical Drives, ICPEED'12,Dec 2012.

- [17] M.N. Uddin, T.S. Radwan, M. Rahman, "Performance of fuzzylogicbased indirect vector control for induction motor drive," IEEE Trans. Ind. Appl. vol. 38, No. 5, pp. 1219–1225, 2002.

- [18] S. Bolognani, M. Zordan, and M. Zigliotto, "Experimental fault tolerant control of a PMSM drive," IEEE Trans. Ind. Electron., vol. 47, no. 5,pp. 1134–1141, Oct. 2000.