# SINGLE DC SOURCE-BASED MULTILEVEL CONVERTER TOPOLOGY WITH REDUCED POWER SWITCHES AND CONDUCTION LOSSES

# Lakshmi KHANDAN K<sup>1</sup>, Andy SRINIVASAN<sup>2</sup>, Mohd.Ali JAGABAR SATHK<sup>3</sup>

<sup>1</sup> Electrical and Electronics Engineering, Adhiparasakthi College of Engineering, Kalavai, Vellore, Tamilnadu, India Tel:+91 9894904203, Email: <a href="mailto:phdlakshmikandan@gmail.com">phdlakshmikandan@gmail.com</a>

<sup>2</sup> Electrical and Electronics Engineering ,Valliammai Engineering College, Chennai, Tamilnadu, India Email: <a href="mailto:itzsrini@yahoo.co.in">itzsrini@yahoo.co.in</a>

<sup>3</sup>Electrical and Electronics Engineering, SRM University, Tamil Nadu India Tel+91 9500525422 Email: jagabarsathik@gmail.com

**Abstract:** Nowadays multilevel inverter with reduced switch count is more attractive among the researchers due to the unsuitability of the conventional multilevel inverter where installation space is constrained. In this category, the marine ship board has limited installation space. In this paper, a new multilevel inverter with reduced power electronics components with improved conduction loss is proposed. The proposed topology is compared with conventional and recent multilevel inverter topologies in terms of the number of levels, auxiliary diode, gate driver circuits, and blocking voltage of switches. The performance of proposed multilevel inverter is measured by using simulation software MATLAB/Simulink, and laboratory workbench-based experimental test has been conducted. Finally, the comparison between the simulation output and experimental result is discussed to prove the superiority of proposed topology.

**Key Words:** Multilevel Inverter, Total Harmonic Distortion, Shipboard, Symmetric topology

#### Introduction

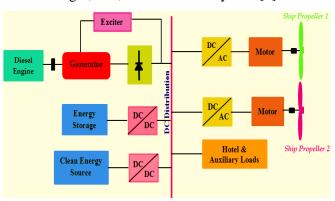

Renewable energy source applications are widely used in all the industries including marine, automobile, traction, and the utility grid. Various renewable energy source applications are available such as photovoltaic (PV) system, wind energy, hydro energy, fuel cell (FC), and biomass. The overview of marine electrical system network is shown in Figure.1. The power converters are playing a major role to control the drive system, communication system, and lighting applications. The electrical system with a combination of ship services and propulsion has significantly reduced the cost and increased the flexibility [1]. Instead of

single blocks for each electrical control unit, the power electronics building block (PEBB) contains all together in a single unit, which leads to reduction in the weight, size, and cost of the system [2].

Figure 1 Schematic Diagram of Ship Propulsion Electrical System

Both DC and AC power converters are used with PWM techniques, which minimizes the harmonics and filter size, but the switching losses are high [3]. Power quality is a major issue among others such as abnormal voltage, frequency variations, harmonics, and transients in a shipboard power plant, which is addressed in [4]. The battery-based shipboard is environmental free, but the size of battery bank will increase the cost of the system. The hybrid energy sources like diesel, photovoltaic, and fuel cell are in conjunction with battery to operate the small- to medium-sized shipboards [5]. Photovoltaic-powered shipboard and issues related to the electrical network are addressed in [6]. A hybrid power system based on PV/FC/diesel generator system is proposed and modeled for green energy and compared with conventional shipboard electrical power generation [7]. The multilevel converters have advantages such as low dv/dt stress, low total harmonic distortion, low electromagnetic interference (EMI), and several multilevel converters for shipboard, and the technical challenges of high-power marine system related to power converter topology are source side power quality and switching device limitations [8]. The conventional multilevel inverter topologies are (i) cascaded H-bridge (CHB), (ii) neutral point clamp (NPC), and (iii) flying capacitor (FC). The drawback of the two-level inverter in shipboards is the design of LC filters for line side, high-power semiconductor devices, high switching frequency, and high common voltage problem [9]. In[10], the suitability of conventional multilevel converter in various applications in shipboard is discussed.

The flying capacitor multilevel converter drive induction motor in shipboard is presented in [11], and this offers better dynamic performance and easy modulation scheme [12]. Even though conventional multilevel converters have numerous advantages, the unique disadvantage of conventional topologies is used in a higher number of switches. Several new multilevel inverter topologies with reduced switches are presented in [13-16]. A diodebased novel multilevel converter topology with electronics components reduced power addressed in [13], and the switches with the series connection of diode are presented. The single dc source with multiple dc-link capacitors bidirectional switches are used to minimize the number of switches in [14]. The unidirectional switch with the parallel connected diode is presented in [15], and also to reduce the high blocking voltage, full bridge inverter is hybrid with proposed topology. Several basic units are connected in cascade for both symmetric and asymmetric configurations as presented in [16] to produce stepped output voltage at the load. In [17], it is proposed for seven levels with reduced switches, but this topology is limited to seven levels if the number of level increases the required number of switch, and power diode also increases with increasing switching pattern complexity. New asymmetrical multilevel converter topology is presented in [18], and also, cascaded topology of proposed converter is discussed. Other than these topologies, several multilevel converters are presented in [19-20]. However, these topologies have unique pros and cons as follows:

- (i) Single DC source (non-isolated DC source) with multiple dc-link capacitors

- (ii) Bidirectional switches

- (iii) Low On-state switches

- (iv) Suitable for PV and wind applications

- (v) Not equal power sharing

- (iv)Various voltage rating switches

However, these topologies require more power semiconductor devices like IGBTs or MOSFET and power diode. In order to minimize the power semiconductor components, in this paper is proposed a novel multilevel converter topology. The following sections are constructed as (i) proposed topology, (ii) mathematical modeling of proposed topology is presented, (iii) various losses associated with proposed multilevel inverter are discussed, (iv) proposed topology with comparison of recent topologies is graphed to show the required number of switches and blocking voltage, (v) to prove the authority of proposed topology, a simulation and experimental-based results are presented, and (vi) finally, the superiority of proposed topology and suitable applications are stated.

## **Proposed Topology**

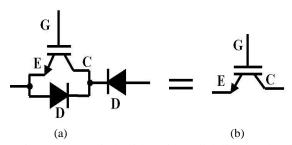

In this section, the construction of proposed symmetric topology with a number of power electronics components is discussed. Figure 1 illustrates the IGBT with the series connection of a diode and without anti-parallel diode switch. Without anti-parallel diode, the switch does not provide a freewheeling path to the current, which introduces a spike at the load, but some topologies are designed as a switch with the series connection of diode that also does not provide freewheeling path except neutral point clamp because of neutral mid-point. Most of the topologies require IGBT with anti-parallel diode, but the topologies shown in Figure 2 use IGBT with anti-parallel diode and series connection of diode. The switched diode multilevel inverter topology also does not provide freewheeling path because unidirectional switches are connected in series with IGBTs.

Figure.2 (a) Switch with anti-parallel diode and series connected diode and (b) switch without anti-parallel diode used in proposed topology

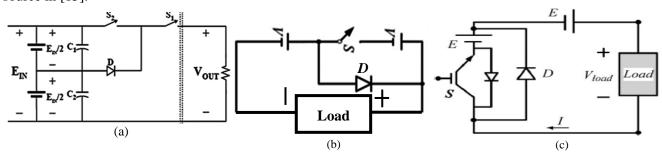

In Figure 3, different basic unit of the multilevel inverter is used in [13],[[15-16]. The proposed topology is recommended to use without antiparallel diode because the conduction losses across the diodes will be reduced double time than [13-16]. In [13], the diodes are placed between the two capacitors and connected with switches. When the switches are turned, the corresponding capacitor voltage will occur at the load and current flow through the diode and switch to the load. The topologies consist of "N" number of dc sources with parallel connected diode except for the first dc source in [15].

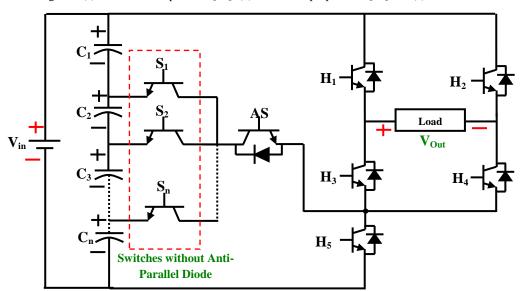

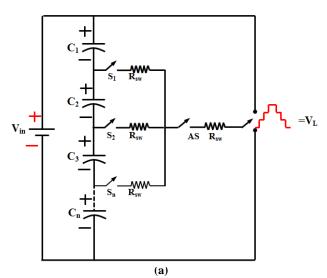

divided into two parts (i) level producer part and (ii) alternator part. The level producer part consists of single dc source ( $V_{in}$ ) with several dc-link capacitors ( $C_1$ ,  $C_2$ .... $C_n$ ) connected to switches without freewheeling diode ( $S_1$ ,  $S_2$ ...... $S_n$ ) in between, and these switches are directly connected with an auxiliary switch (AS) as shown in Figure.4. The auxiliary switch (AS) consists of the anti-parallel diode to provide the continuous current path in zero states. The generalized switching sequence for "m" number of levels is listed in Table.1, and the sequence is presented for "2N+1" levels.

Figure.3 (a) Basic Unit Proposed in [13], (b) Basic Unit proposed in [15] and (c) Presented basic unit in [16]

Figure.4 Generalized Structure of Proposed MDCC Multilevel Inverter

These topologies are configured for both symmetric and asymmetric configurations. The proposed topology is only suitable for symmetric configuration, so the symmetric configuration of other topologies is only considered in this paper. Here it is worth to mention that proposed topology requires less number of power electronics components than other topologies. The proposed converter uses a lower number of switches to obtain a higher number of levels, and this topology is

This proposed multilevel inverter is called as multiple DC-link capacitor-based multilevel inverter (MDCC MLI) topology. The  $V_{\rm in}$  value is equally divided into each capacitor such as  $V_{\rm in}/N$ , where N is the number of capacitors. Each dc-link source magnitude is equal since this topology is only suitable for symmetric configuration. The nature of a capacitor will not maintain the equal voltage among the each capacitor, so the voltage balancing circuit is required [21] for proposed topology.

Alternator part requires four switches  $(H_1-H_4)$  that are capable of high blocking voltage to produce synthesized stepped positive and negative output voltages  $(0, \pm C_1, \pm C_2, \ldots, \pm C_n)$  at the load.

$= (3N^2+1)/4$  for odd number of N where "N" is the number of dc-link capacitors. The comparison of proposed and conventional H-bridge multilevel inverters for symmetric configuration is

Table 1. Switching Sequence for Proposed Topology

| Level | Switches OFF                                                                                      | Switches ON                                                                      | Output Voltage                     | Number of<br>On-State |

|-------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------|-----------------------|

| 0     | H <sub>3</sub> ,H <sub>4</sub> ,H <sub>5</sub> or H <sub>1</sub> ,H <sub>2</sub>                  | H <sub>1</sub> ,H <sub>2</sub> or H <sub>3</sub> ,H <sub>4</sub> ,H <sub>5</sub> | 0                                  | 2 or 3                |

| 1     | $H_2,H_3,H_5$ $S_2S_n$                                                                            | H <sub>1</sub> ,H <sub>4</sub> , AS,S <sub>1</sub>                               | +C <sub>1</sub>                    | 4                     |

| 2     | $H_1,H_4,H_5$ $S_2S_n$                                                                            | H <sub>2</sub> ,H <sub>3</sub> ,AS,S <sub>1</sub>                                | -C <sub>1</sub>                    | 4                     |

| 3     | $H_2,H_3,H_5 S_1,S_3S_n$                                                                          | H <sub>1</sub> ,H <sub>4</sub> , AS,S <sub>2</sub>                               | +C <sub>1</sub> +C <sub>2</sub>    | 4                     |

| 4     | $H_1, H_4, H_5, S_1, S_3 S_n$                                                                     | H <sub>2</sub> ,H <sub>3</sub> ,AS,S <sub>2</sub>                                | -(C <sub>1</sub> +C <sub>2</sub> ) | 4                     |

| 5     | $H_2,H_3,H_5,S_1,S_2,S_4S_n$                                                                      | H <sub>1</sub> ,H <sub>4</sub> , AS,S <sub>3</sub>                               | $+C_1+C_2+C_3$ )                   | 4                     |

| 6     | $H_1, H_4, H_5, S_1, S_2, S_4 \dots S_n$                                                          | H <sub>2</sub> ,H <sub>3</sub> ,AS,S <sub>3</sub>                                | $-(C_1+C_2+C_3)$                   | 4                     |

| ÷     | :                                                                                                 | :                                                                                | :                                  | :                     |

| :     | :                                                                                                 | :                                                                                | :                                  | :                     |

| 2N    | H <sub>2</sub> ,H3,H <sub>5</sub> S <sub>1</sub> ,S <sub>3</sub> S <sub>n</sub>                   | H <sub>1</sub> ,H <sub>4</sub> ,S <sub>5</sub>                                   | $+\sum_{i=1}^{n}C_{n}$             | 3                     |

| 2N+1  | H <sub>1</sub> ,H <sub>4</sub> ,H <sub>5</sub> ,S <sub>1</sub> ,S <sub>2</sub> ,S <sub>4</sub> Sn | $\mathrm{H}_2,\!\mathrm{H}_3,\!\mathrm{S}_5$                                     | $-\sum_{i=1}^{n}C_{n}$             | 3                     |

The  $C_n$  capacitor is connected to the load through switch  $H_5$  remaining in all the capacitors that are connected through AS and switches  $(S_1-S_n)$ . The number of output voltage levels $(N_{Level})$ , number of IGBTs with anti-parallel diode  $(N_{IGBT,D})$ , number of IGBTs without anti-parallel diode $(N_{IGBT})$ , number of gate drive circuits $(N_{Gate})$ , and total blocking voltage of proposed inverter are discussed as follows:

The number of levels based on the dc-link capacitor is expressed in equation (1)

$$N_{\text{Level}} = 2N + 1 \tag{1}$$

Number of IGBTs with and without diode can be calculated by using equations (2) & (3)

$$N_{IGBT} = N-1$$

(2)

$$N_{IGBT,D} = 6 \tag{3}$$

The total number of IGBTs is considered as switches and can be evaluated as follows:

$$N_{\text{Switch}} = N + 5$$

(4)

The required number of gate driver circuits and total blocking voltage are expressed in equations (5) & (6)

$$N_{Gate} = N + 5 \tag{5}$$

$$T_{Block} = V_{dc} * (P+2N)$$

(6)

where  $P = 3N^2/4$  for even number of N

Table.2 Comparison of proposed and cascaded H-bridge multilevel inverters for symmetric

| configuration                                     |                                                                                                         |                     |  |  |  |  |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------|--|--|--|--|

| Description                                       | Proposed                                                                                                | СНВ                 |  |  |  |  |

| Number of IGBTs<br>without anti-parallel<br>diode | N-1                                                                                                     | -                   |  |  |  |  |

| Number of IGBTs<br>with anti-parallel<br>diode    | 6                                                                                                       | 4*N                 |  |  |  |  |

| On-state switches                                 | 4                                                                                                       | 2*N                 |  |  |  |  |

| Total blocking voltage                            | $V_{dc}$ * (P+2N)<br>Where P= $3N^2/4$ for<br>even number of N<br>= $(3N^2+1)/4$ for odd<br>number of N | 4*N*V <sub>dc</sub> |  |  |  |  |

| Number of DC source                               | 1                                                                                                       | N                   |  |  |  |  |

| Number of DC-link capacitors                      | N                                                                                                       | -                   |  |  |  |  |

| Maximum output voltage                            | $N*V_{dc}$                                                                                              | N*V <sub>dc</sub>   |  |  |  |  |

| Gate driver circuits                              | N+5                                                                                                     | 4*N                 |  |  |  |  |

listed in Table.2. Comparison of the number of switches, state switches, blocking voltage, and gate driver circuits is presented. It is evident that proposed topology uses a lower number of switches for a higher number of level.

#### **Modeling of Proposed Multilevel Inverter**

A state space mathematical model representation of any system comprises a set of input, output, and state variables state space model is a more flexible and convenient method to model and

$$V_{L} = R_{sw} i_{L}(t) + R_{L} i_{L}(t) + L \frac{di_{L}(t)}{dt}$$

(9)

where  $R_L = R + R_{ind}$  and R,  $R_{ind}$ ,  $R_{SW}$ , and L are the total load resistance in ohms, the load resistance in ohms, the internal resistance of a load inductor in ohms, the ON-state resistance of the total conducting IGBTs in each level, and the load inductance in mH, respectively. In this topology, in each level, the number of conducting components is

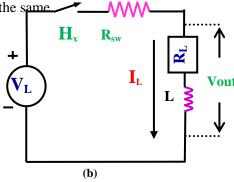

Figure.5 (a) Topology of MDCC (b) simplified circuit for state space model

analyze systems with "n" number of inputs and outputs. Consider  $S_1,\ S_2,\ S_3,...AS$ , and  $H_5$  be the signals for each level of output to the 9-level inverter. A simplified model and equivalent circuit of the proposed multilevel inverter is represented in Figure.5. The Figure.5a,  $S_1...S_n$  are switched with internal resistance ( $R_{SW}$ ), the  $V_L$  level generator output voltage, which is positive output cycle. In Figure. 5b, the Hx and Rsw are the full-bridge switch sand resistance and L and  $R_L$  are load inductance and resistance.

Let

$$B = \begin{cases} 1 & \text{for positive half cycle} \\ -1 & \text{for negative half cycle} \end{cases}$$

(7)

The variable "F" is the realization of the full bridge in the proposed topology; the Sx and  $R_{SW}$  are switch and switch resistance, respectively. Therefore, the net output  $V_L$  from the m-level inverter is given by:

$$V_{L} = \begin{bmatrix} 1 & 1 & 1 & 1 \end{bmatrix} \begin{bmatrix} B_{1}F \\ B_{2}F \\ B_{3}F \\ B_{4}F \end{bmatrix} [V_{dc}]$$

(8)

where  $V_{dc}$  is the magnitude sum of each dc source and  $B_1$  to  $B_4$ is the comparator output signal (binary output). By applying KVL to the circuit:

$$L\frac{di_{L}(t)}{dt} = \begin{bmatrix} 1 & 1 & 1 & 1 \end{bmatrix} \begin{bmatrix} B_{1}F \\ B_{2}F \\ B_{3}F \\ B_{4}F \end{bmatrix} [V_{dc}] - (R_{sw} + R_{L})i_{L}(t)$$

(10)

Let the state variable be the current through the inductor  $x=i_L(t)$  and input variable  $u=V_L$ :

$$\frac{di_{L}(t)}{dt} = \frac{\begin{bmatrix} 1 & 1 & 1 & 1 \end{bmatrix} \begin{bmatrix} B_{1}F \\ B_{2}F \\ B_{3}F \\ B_{4}F \end{bmatrix}}{L} [V_{dc}] - (R_{sw} + R_{L})i_{L}(t)}$$

(11)

where

$$\mathbf{x} = \frac{d\mathbf{i}_{L}(t)}{dt}$$

;

$\mathbf{A} = \begin{bmatrix} 1 & 1 & 1 \end{bmatrix} \begin{bmatrix} \mathbf{B}_{1}\mathbf{F} & \mathbf{B}_{2}\mathbf{F} & \mathbf{B}_{3}\mathbf{F} & \mathbf{B}_{4}\mathbf{F} \end{bmatrix}^{T}$

$\mathbf{B} = -(\mathbf{R}_{sw} + \mathbf{R}_{L})$

Similarly, the voltage across the load is given by the expression:

$$V_{\text{out}} = R_{\text{L}} i_{\text{L}}(t) + L \frac{\text{di}_{\text{L}}(t)}{\text{dt}}$$

(12)

where

$$y = V_{out}$$

;  $C = (R_L + L\frac{d}{dt})$ ; and  $D = 0$

In general, the state space switched model of the proposed topology is given by:

$$\frac{di_{L}(t)}{dt} = \frac{\left[A\right] \begin{bmatrix} B_{1}F & \cdots & B_{k}F \end{bmatrix}^{T} \begin{bmatrix} V_{dc} \end{bmatrix} - (R_{sw} + R_{L})i_{L}(t)}{L}$$

(12)

Where the dimension of [A]=1  $\times$  (N<sub>level</sub> -1)/2, k varies from 1 to (N<sub>level</sub> -1)/2, Vdc is the magnitude of each dc source, and i<sub>L</sub>(t) is the current through the inductor. The generalized state space switched model is explained in equation (13), and it is applicable for proposed asymmetric topology with any number of levels. The various operating mode of proposed topology for nine-level inverter is illustrated in Figure.6. In this, the switches S<sub>1</sub>......S<sub>n</sub> will be turned ON and OFF one time for each half cycle with auxiliary switch and full bridge switches either (H<sub>1</sub>& H<sub>3</sub>) or (H<sub>2</sub>& H<sub>4</sub>) pair. The positive cycle and negative cycle of current flow are indicated in red and blue colors, respectively.

#### Loss In Proposed MDCC MLI

The switching and conduction losses [13] are a major loss in the multilevel converter, and also the proposed topology consists of multiple dc-link capacitors, so the loss of capacitors is also taken into account.

#### A. Loss in Switch Conduction Mode

#### (i) Conduction Loss

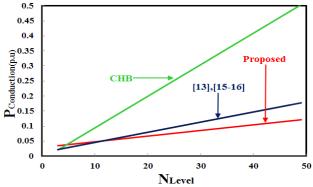

The duration of ON period of switches is taken into account, and the voltage drop across the switch during on period is based on the semiconductor used in the switch, and this is available from manufacturer datasheet. Conduction losses are calculated for both IGBTs ( $P_{C,T}$ ) and anti-parallel diode ( $P_{C,D}$ ) as in equation (14). It is evident that proposed topology produces low conduction loss because it does not require anti-parallel diode-based switches except six switches. The resistance on the semiconductor and voltage drop is multiplied with current through the switches as given in expressions (15) and (16).

$$P_{\rm C} = P_{\rm C,T} + P_{\rm C,D} \tag{14}$$

$$P_{C,T=}[V_{on,T}(t)+R_T.I^{\beta}(t)].I(t)$$

(15)

$$P_{CD} = [V_{onD}(t) + R_D I(t)] I(t)$$

(16)

$\beta$ - is the constant specification-related transistor, and it is available from manufacturer datasheet,  $V_{\text{on},T}$  and

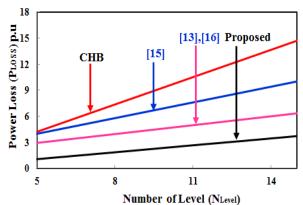

$V_{\text{on,D}}$  are the constant parameters, on state voltage of transistor and diode, respectively. The advantage of proposed topology is low conduction losses because the switches S1...Sn do not have the anti-parallel diode. The comparison of conduction loss and other topologies is illustrated in the graph as shown in Figure.7.

Figure.7 Conduction Loss Vs Number of Level (ii). Switching Loss

The expression for energy loss during the turn on  $(E_{ON})$  and turn off  $(E_{OFF})$  of switches is:

$$E_{OFF} = \frac{V_{off} \cdot I.t_{off}}{6}$$

(17)

$$E_{\rm ON} = \frac{V_{\rm off} . I.t_{\rm on}}{6} \tag{18}$$

where  $t_{\text{on}}$  and  $t_{\text{off}}$  are on and off state time of switches,  $V_{\text{off}}$  is voltage across the switches in off state.

$$P_{SW} = 2f(E_{ON} + E_{OFF})$$

(19)

The above equations (17) and (18) give energy losses for one switch, and the resultant equation (19) gives switching loss of single switch, in order to calculate the switching losses for all the switches presented in multilevel inverter of the equation (20) used.

$$P_{SW} = 2f(\sum_{i=1}^{n} E_{ON,i} + E_{OFF,i}),$$

(20)

Where n- is the last switch of the proposed multilevel inverter.

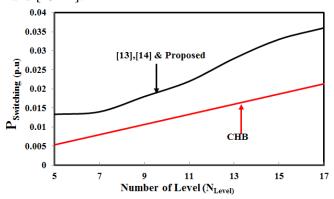

However, both conduction and switching losses depend on the voltage and current ratings of switches, but in recent topologies, the voltage rating of switches is variable and current is equal in all the switches. The voltage ratings of switches are chosen based on the blocking voltage across the switches. In this paper, the switching losses are not provided because the proposed topology requires a minimum number of switches and operates under fundamental switching modulation techniques. The proposed topology uses a low number of switches compared

to topologies [13-16]. Figure.8 depicts the switching loss of proposed topology against a number of levels. The energy loss during turn on and turn off is directly proportional to the blocking voltage from this, if the blocking voltage increases, the switching loss also increases. Conventional CHB has low blocking voltage compared to proposed topology and [13-14].

Figure.8 Switching Loss Vs Number of Level

## B. Capacitor loss

In power electronics, circuit's most common failure components is a dc-link capacitor, which has losses based on heat dissipation and reduces the reliability of the system. The major capacitor losses are due to voltage stress, excessive operating voltage, reverse voltage, and excessive ripple current. These factors are an influence to increase dissipation factors of the capacitors as presented in [22], and capacitor design is considered based on reliability, and life time capacitor is based on their applications [23]. In this paper, the capacitor losses are not considered because all the topologies require same number of DC-link capacitors in input side.

tan

$$\delta = \frac{R}{1/\omega C} = \omega CR$$

(21)

$\omega = 2\pi f, \pi - \text{Circular Constant, f - Frequency}$

w 2/11,11 enreum constant, i frequency

R- Equivalent series resistance of capacitor

The total power losses in proposed topology is

$$P_{LOSS} = P_C + P_{SW} + P_{CAP} \tag{22}$$

Figure.9 illustrates the comparison of total power loss excluding the capacitor loss because the capacitor loss in all the topology is same.

Fig.9 Number of Level ( $N_{\rm Level}$ ) Vs Power Loss ( $P_{\rm Loss}$ ) Figure.9 illustrates the comparison of total power loss excluding the capacitor loss because the capacitor loss in all the topology is same. In general, the switching loss value is lower than the conduction loss. In this, CHB has high conduction loss due to large number of on time switches and diode. The proposed topology may produce high switching loss, but the conduction loss is low, which further reduces the total power loss.

# **Comparison with Other Topologies**

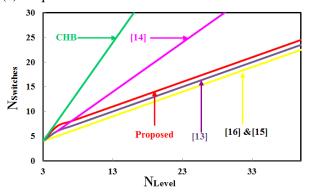

(a) Required Number of Switches

Figure.10 Number of Switches Vs Number of Level

The superiority of proposed topology can be proved by comparing the topologies [13-16] and CHB; the number of switches and number of level is shown in Figure.10. The topologies [13],[15] and [16] use a low number of switches because the dc source is connected with series of IGBT and parallel/series to the diode. The conventional CHB presented in [14] requires a higher number of switches than the proposed.

(b) Required Number of Power Semiconductor Devices

| Table 3 Comparison of number of power components required for 9-level inverter |                     |          |      |      |      |      |     |

|--------------------------------------------------------------------------------|---------------------|----------|------|------|------|------|-----|

| S.No                                                                           | Description         | Proposed | [13] | [14] | [15] | [16] | СНВ |

| 1.                                                                             | Number of switches  | 9        | 8    | 10   | 7    | 7    | 16  |

| 2.                                                                             | Anti-parallel diode | 6        | 8    | 10   | 7    | 7    | 16  |

| 3.                                                                             | Number of Diode     | -        | 3    | -    | 3    | 3    | -   |

|                                                                                | Total Number of     | 15       | 19   | 20   | 17   | 17   | 32  |

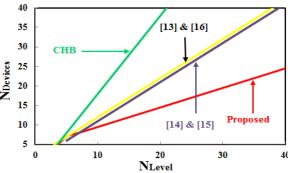

Another important parameter related to reliability is a total number of devices used in the circuit. Figure .11 illustrates the total number of devices against a number of levels. This proposed topology requires a minimum number of devices (IGBT and power diode) compared to all other devices. As the number of devices increases, the reliability of the inverter will be degraded. Table.3 presents the detailed components required for a 9-level inverter with each topology.

Figure.11 Number of Power Semiconductor Devices Vs Number of Level

The topologies [15-16] and proposed topology require a minimum number of power electronics components such as number dc-link capacitor, power diode, and switches. In general, the conduction loss value is higher than the switching loss; here it is worth to mention that proposed topology requires a minimum conduction loss compared to [15-16]. To reduce the switching loss, various modulation techniques are proposed [24], but for conduction loss, the semiconductor device has to change or reduce the components, hereby reducing the components by achieving the low conduction losses.

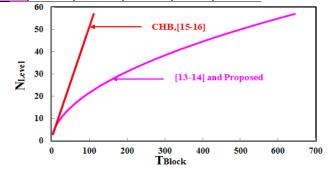

#### (c)Total Blocking Voltage

The withstanding voltage across the switches will be varying to each structure of multilevel inverter topology.

Figure.12 Number of Level vs Total Blocking Voltage

The total blocking voltage is the sum of voltage across all the switches that are taken into account; the topologies presented in [15-16] use an isolated dc source in which switch's blocking voltage is equal to each dc sources connected with them, but in the case proposed, [13-14] structures are developed based on single dc sources as shown in Figure.12. This will increase the blocking voltage across the switches. However, the proposed topology uses a lower number of power semiconductor devices and low conduction losses.

### **Simulation and Experimental Results**

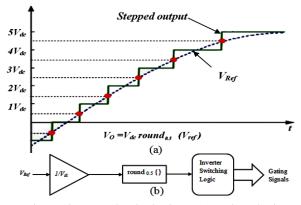

Figure.13 Nearest level selection: (a) Level synthesis

To verify the performance of proposed topology, the simulation and experimental results are presented for a 9-level inverter. The fundamental switching (50Hz) method called nearest level modulation (NLM) technique as illustrated in Figure.13 is used in both simulation and hardware. NLM technique has low switching frequency which produces low switching loss compared to carrier-based techniques. The output modulation voltage frequency is 50Hz, and all DC/AC power converters paid more attention to the total harmonics distortion (THD). The THD equation for the sinusoidal waveform is expressed in equation (23).

THD =

$$\sqrt{\frac{\sum_{h=3,5,7....}^{\infty} V_{oh}}{V_{o1}}} = \sqrt{\left(\frac{V_{orms}}{V_{o1}}\right)^2 - 1}$$

(23)

In equation (23), h (odd order of the harmonic) =3, 5, 7.... and  $V_{o1}$  fundamental of the output voltage.  $V_{oh}$  order harmonic.  $V_{o,rms}$ -is the rms value of the output voltage. The magnitude of the  $V_{o1}$  and  $V_{o,rms}$  can be calculated using the following relations:

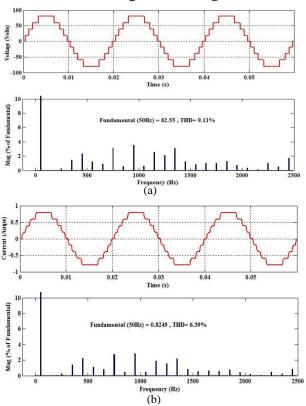

Figure.14 Simulation output results for (a) output voltage waveform and (b) current waveform

$$V_{orms} = \frac{2\sqrt{2}V}{\pi} \times \sqrt{\sum_{h=odd}^{\infty} \left(\sum_{j=1}^{N_{Level}} \frac{cos(h\theta_j)}{h}\right)^2}$$

(24)

$$V_{o1} = \frac{2\sqrt{2}V}{\pi} \times \left(\sum_{j=1}^{N_{Level}} \frac{\cos(h\theta_j)}{h}\right)$$

(25)

where the values of  $\theta 1$ ,  $\theta 2...\theta_{NLevel}$  are switching angles and are calculated by the following equation:

$$\theta_{\rm j} = \sin^{-1} \left( \frac{\rm j - 0.5}{\rm N_{\rm Level}} \right) \rm j = 1, 2, 3 .... N_{\rm Level}$$

(26)

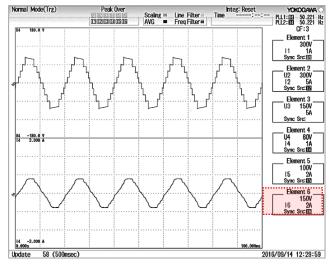

Figure.15 Experimental output Voltage and Current Waveform

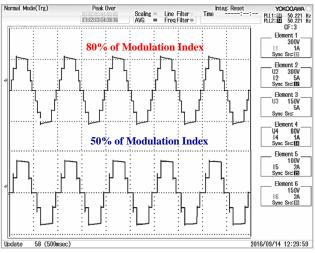

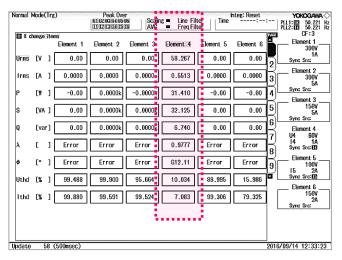

Equations (24), (25), and (26) confirm that output voltage THD depends on a number of output levels and switching angle. The simulated proposed 9-level inverter output voltage and current waveform are shown in figures.14 a and b, respectively. The voltage across each dc-link capacitor is 20V. The simulation output voltage THD is 9.11% and current THD is 6.39% for  $R=100\Omega$  and L=12mH, respectively. The current THD depends on the load value if highly inductive, the inductive will act as a low-pass filter and produce a sinusoidal waveform. The experimental output voltage and current waveform are shown in Figure.15. In this, IGBT BUP400D switches, maximum V<sub>ce</sub> of 600V, and maximum current Ic of 22A are used. The required number of switches for the 9-level inverter is 9 switches with 9 gate driver circuits. In simulation and experimental, the input voltage and load R-L values are kept as same. It is observed that both simulation and experimental have a good agreement in terms of THD and output values. By keeping the modulation index as 80%, the output voltage level across the load is reduced to 7 levels, and 50% of modulation index produces a 5-level output voltage at the load as shown in Figure.16. The experimental results of voltage and current RMS value, total harmonics distortion for both voltage and current are presented in Figure 16. The THD value of both voltage and current are 10.034 % and 7.083 %, respectively, which is in good agreement with simulation value. The theoretical value of RMS voltage for peak value of 80V is 56.56 V, in

simulation results 58.67, but in experimental 58.2V, which is once again confirming that proposed topology has good agreement with simulation and produces better results.

Figure.16 Experimental output Voltage Waveform for 80% and 50% modulation index

Figure 17. Experimental Power quality analyzer results of proposed 9-level inverter

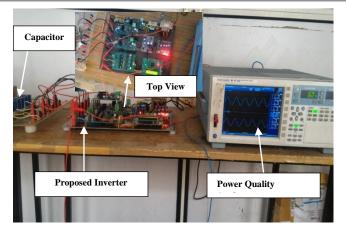

The FPGA controller is used to generate the switching pulses, the output of controller is fed to the isolation circuit (optocoupler) and driver circuit to enhance the driving. The photograph of the experimental setup is shown in Figure.18 with the digital storage oscilloscope is presented and the experimental voltage and current waveforms are presented. In this FPGA Spartan, theXE3S250E controller is used to generate the switching pulses for the 9-level inverter. The efficiency of proposed topology is listed in Table.4.

Table. 4 Various Parameters measured in proposed 11-level inverter for R=100Ohm and L=12mH

| Results      | Vrms<br>(V) | Irms<br>(A) | V<br>THD<br>(%) | I<br>THD<br>(%) | Pin<br>(W) | Pout<br>(W) | Efficiency η (%) |

|--------------|-------------|-------------|-----------------|-----------------|------------|-------------|------------------|

| Simulation   | 58.60       | 0.59        | 9.11            | 6.39            | 34.57      | 34.00       | 98.34            |

| Experimental | 58.26       | 0.55        | 10.03           | 7.083           | 32.04      | 31.41       | 98.03            |

Figure.18 Photograph of Experimental Workbench Conclusion and Future Scope of Work

In this study, a new single dc source with multiple dc-link capacitors based on symmetric multilevel inverter structure is developed. The anti-parallel diode and without diode-based switches are used, which minimizes the conduction losses. proposed topology produces low power loss compared to other topologies for the same number of output voltage levels and it requires lower number of the power semiconductor devices, which leads to reduction in layout size, simple switching pattern, and high efficiency. Total blocking voltage of proposed topology is equal to [13-14], but higher than the CHB. Hence, the performance and efficiency of the proposed 9-level inverter are verified by both simulation and experimental results. It is evident that the proposed topology is more suitable for shipboard applications because single dc source can be used to drive the shipboard propulsion motor. The full-bridge inverter switches should withstand the maximum voltage, which increases the cost, and in order to reduce the maximum voltage, cascaded blocking structure recommended, and this is considered as a future scope of work.

#### References

1. McCoy, T.J., 2002, July. Trends in ship electric propulsion. *In Power Engineering Society Summer Meeting*, 2002 IEEE (Vol. 1, pp. 343-346).

- Ericsen, T., Hingorani, N. and Khersonsky, Y., 2006, September. PEBB-Power Electronics Building Blocks from concept to reality. *IEEE Industry Applications Society 53rd Annual Petroleum and Chemical Industry Conference (pp. 1-7)*.

- 3. Ericsen, T., Hingorani, N. and Khersonsky, Y., 2004, September. Power electronics and future marine electrical systems. *Petroleum and Chemical Industry Technical Conference*, 2004. *Fifty-First Annual Conference* 2004(pp. 163-171).

- 4. Barros, J. and Diego, R.I., 2016. A review of measurement and analysis of electric power quality on shipboard power system networks. Renewable and Sustainable Energy Reviews, 62, pp.665-672.

- 5. Trovão, J.P., Machado, F. and Pereirinha, P.G., 2016. Hybrid electric excursion ships power supply system based on a multiple energy storage system. *IET Electrical Systems in Trans*.

- 6. Guo, C., Sun, Y., Yuan, C., Yan, X., Wang, Y. and Jiang, Q., 2015, November. Research on power load flow calculation for photovoltaic-ship power system based on PSAT. International Conference on Renewable Energy Research and Applications (ICRERA) (pp. 443-448).

- Banaei, M.R. and Alizadeh, R., 2016. Simulation-Based Modeling and Power Management of All-Electric Ships Based on Renewable Energy Generation Using Model Predictive Control Strategy. *IEEE Intell.Trans.Sys.Mag*, 8(2), pp.90-103.

- 8. Thantirige, K., Rathore, A.K., Panda, S.K., Jayasignhe, G., Zagrodnik, M.A. and Gupta, A.K., 2015, March. Medium voltage multilevel converters for ship electric propulsion drives. *International Conference on Electrical Systems for Aircraft, Railway, Ship Propulsion and Road Vehicles* (ESARS)(pp. 1-7).

- Abu-Rub, H., Lewicki, A., Iqbal, A. and Guzinski, J., 2010, July. Medium voltage drives-challenges and requirements. In 2010 IEEE International Symposium on Industrial Electronics (pp. 1372-1377).

- Wang, F., Zhang, Z., Ericsen, T., Raju, R., Burgos, R. and Boroyevich, D., 2015. Advances in Power Conversion and Drives for Shipboard Systems. Proceedings of the IEEE, 103(12), pp.2285-2311.

- 11. Sáiz, V.M.M. and López, A.P., 2007. Future trends in electric propulsion systems for commercial vessels. *Journal of Maritime Research*, 4(2), pp.81-100.

- 12. Reusser, C.A. and Young, H., 2015, March. Full electric ship propulsion based on a flying capacitor converter and an induction motor drive. *International Conference on Electrical Systems for Aircraft, Railway, Ship Propulsion and Road Vehicles* (ESARS) (pp. 1-6).

- 13. R. Samanbakhsh and A. Taheri, "Reduction of Power Electronic Components in Multilevel Converters Using New Switched Capacitor-Diode Structure," in *IEEE Trans.Ind.Electron.* vol. 63, no. 11, pp. 7204-7214, Nov. 2016.

- 14. Alishah, R.S., Nazarpour, D., Hosseini, S.H. and Sabahi, M., 2015. Reduction of power electronic elements in multilevel converters using a new cascade structure. *IEEE Trans.Ind.Electron*, 62(1), pp.256-269.

- 15. Alishah, R.S., Nazarpour, D., Hosseini, S.H. and Sabahi, M., 2014. New hybrid structure for multilevel inverter with fewer number of components for high-voltage levels. *IET Power Electronics*, 7(1), pp.96-104.

- Alishah, R.S., Nazarpour, D., Hosseini, S.H. and Sabahi, M., 2014. Novel topologies for symmetric, asymmetric, and cascade switched-diode multilevel converter with minimum number of power electronic components. *IEEE Trans. Ind. Electron*, 61(10),pp. 5300-5310.

- 17. Choi, J.S. and Kang, F.S., 2015. Seven-Level PWM Inverter Employing Series-Connected Capacitors Paralleled to a Single DC Voltage Source. IEEE Trans. Ind. Electron., 62(6), pp.3448-3459.

- 18. Kangarlu, M.F. and Babaei, E., 2013. A generalized cascaded multilevel inverter using series connection of submultilevel inverters. *IEEE trans.power electron.*, 28(2), pp.625-636.

- 19. Ceglia, G., Guzman, V., Sanchez, C., Ibanez, F., Walter, J. and Gimenez, M.I., 2006. A new simplified multilevel inverter topology for DC&AC conversion, *IEEE Trans.power electron.*, 21(5), pp.1311-1319.

- 20. Gautam, S.P., Sahu, L.K. and Gupta, S., 2016. Reduction in number of devices for symmetrical and asymmetrical multilevel inverters. *IET Power Electronics*, 9(4), pp.698-709.

- 21. R. S. Alishah, S. H. Hosseini, E. Babaei and M. Sabahi, "A New General Multilevel Converter Topology Based on Cascaded Connection of Submultilevel Units With Reduced Switching Components, DC Sources, and Blocked Voltage by Switches," *IEEE Trans. Ind. Electron*, vol. 63, no. 11, pp. 7157-7164, Nov. 2016.

- 22. Wang, H. and Blaabjerg, F., 2014. Reliability of capacitors for DC-link applications in power electronic converters—An overview. *IEEE Trans. Ind. Appl.*, 50(5), pp.3569-3578.

- 23. Technical note: judicious use of aluminum capacitors, Nippon Chemi-Con Corporation

- E. Villanueva, P. Correa, J. Rodriguez, and M. Pacas, "Control of a single-phase cascaded H-bridge multilevel inverter for grid-connected photo-voltaic systems, "IEEE Trans. Ind. Electron., vol. 56, no. 11, pp. 4399-4406, Nov. 2009.